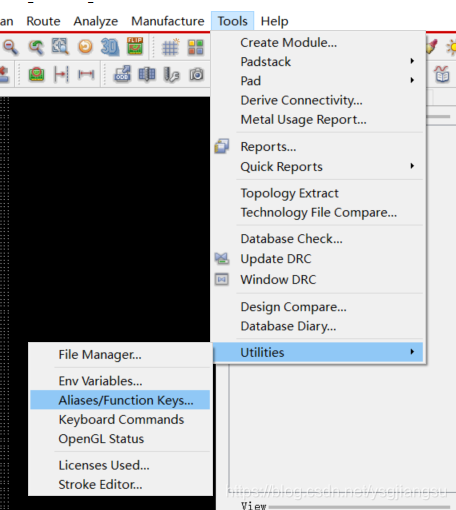

source $TELENV

funckey A mirror

funckey F9 grid toggle

funckey F10 zoom fit

funckey F11 zoom in

funckey F12 zoom out

funckey M move

funckey m move

funckey w add connect

funckey W add connect

funckey Del delete

funckey ' ' iangle 45

funckey ~M show measure

funckey ~S save

funckey ~Z undo

### User Preferences section

### This section is computer generated.

### Please do not modify to the end of the file.

### Place your hand edits above this section.

###

set padpath = $padpath D:/SoftWare/CadenceLib/abt/ D:/SoftWare/CadenceLib/others/Heijinlib/

set psmpath = $psmpath D:/SoftWare/CadenceLib/abt/ D:/SoftWare/CadenceLib/others/Heijinlib/

在哪里查看设置结果呢:

弹出的 对话框 就是了。

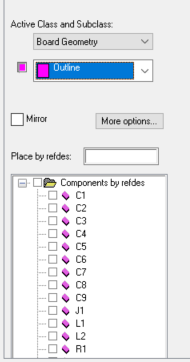

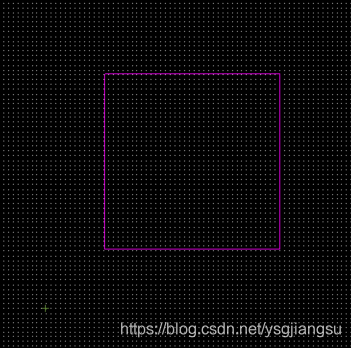

先给PCB圈块地,也就是outline

建议用命令行搞

x 0 0

ix 30

iy 30

ix -30

iy -30

30mmx30mm的板子就定下来了

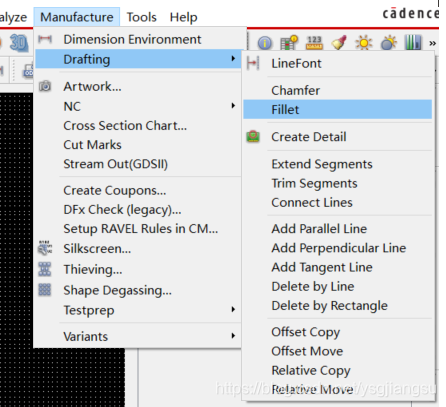

觉得矩形锋利?添加倒角,不需要你自己画圆的

依次点击需要倒角的两根线,即可

各自为政,互补干涉,但是组内逻辑都是 类 似的。

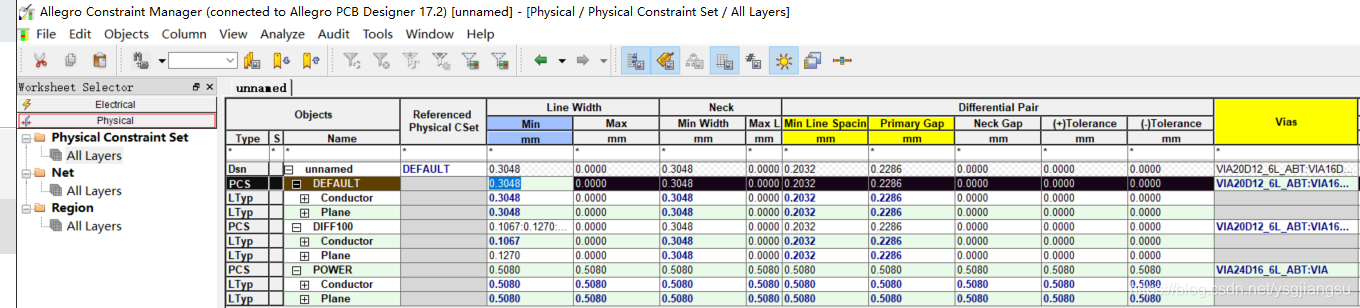

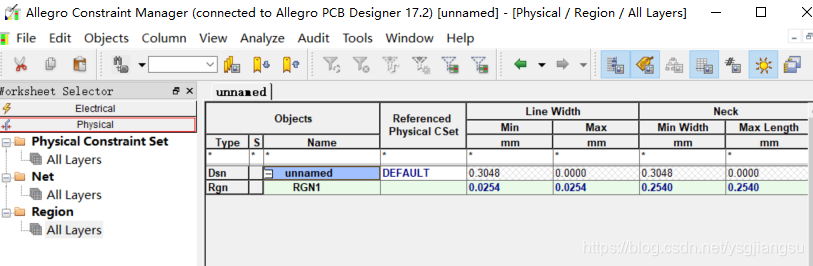

比如:我们可以先设置集合SET:default、diff100、power等等

然后分别设置集合的特性,所谓特性就是线宽最大最小,neck最大最小,可用的VIA封装(插一句,neck是干嘛的?neck一般要比line小一些。目的是在狭小空间走线时,line走不下,切换到neck模式下走,然后再恢复line)

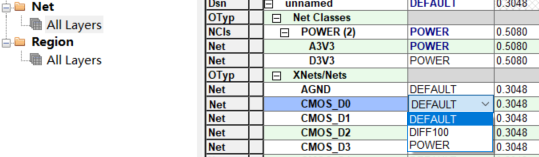

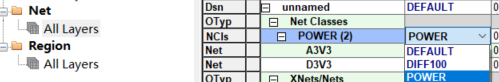

这样的话,我们在NET栏就能选择某根线所属集合了,集合就决定了属性

但是,我觉得我不想一个个设置电源走线,可以建个电源类,然后属性赋值想要的集合就行(赤果果的C++啊)

注意这里POWER类与集合POWER一点关系没有,只是名字都叫POWER

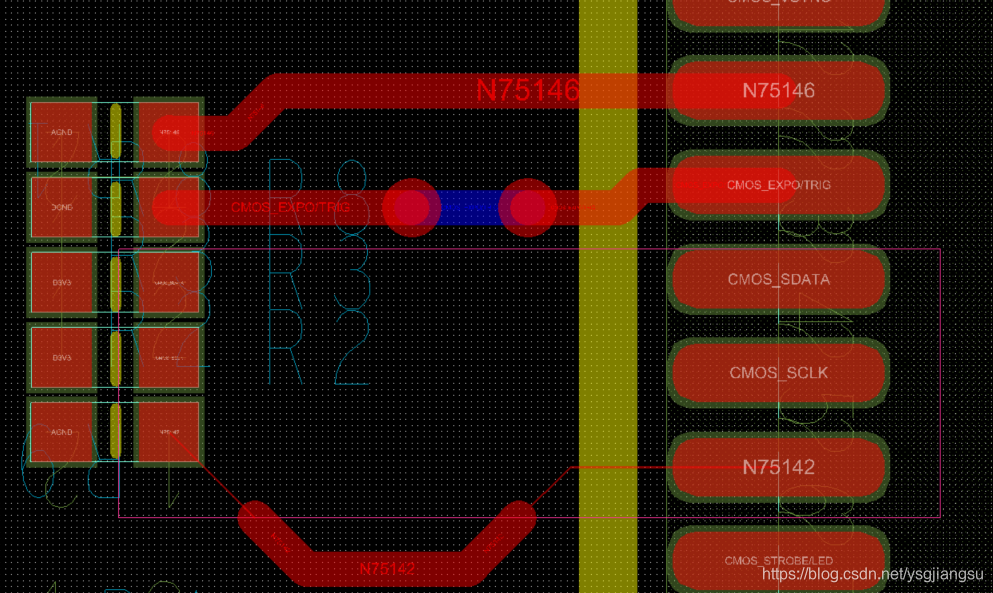

还有一个Region干嘛的?

就是设置一个region集合,该集合的属性会 屏蔽 之前的属性设置,或者说全局的属性设置。效果就是在region内部,按region的规矩来,离开了就按正常的规矩来。所以就是上图看到的样子。

看看我是如何设置的:

右键unnamed,create–>region,名字自定,填写参数。保存退出。

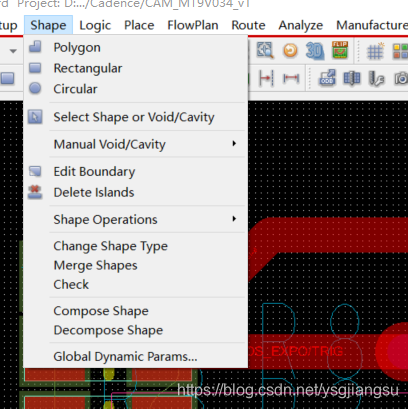

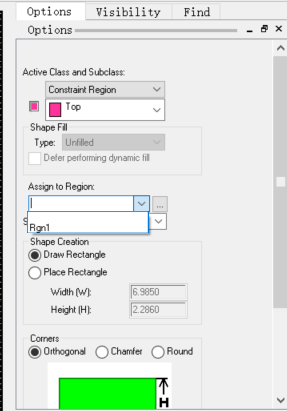

画几何图形,选择constraint region,在assign to region下选择刚刚定义的region,然后画个框就行了。

约束是为了更好的管理,cadence通过约束,更好的规范了工程师的行为,提高了效率。但是本篇介绍的CM,只是皮毛,还有很多细节,写不下了,先到这里吧

免责声明:本文系网络转载或改编,未找到原创作者,版权归原作者所有。如涉及版权,请联系删