作为Cadence学习者的新手,有很多细节需要注意,大致走了一下流程,将其中一些步骤记录下来,也方便以后自己查看,当然软件版本界面可能略有不同。

使用软件是Cadence17.4.

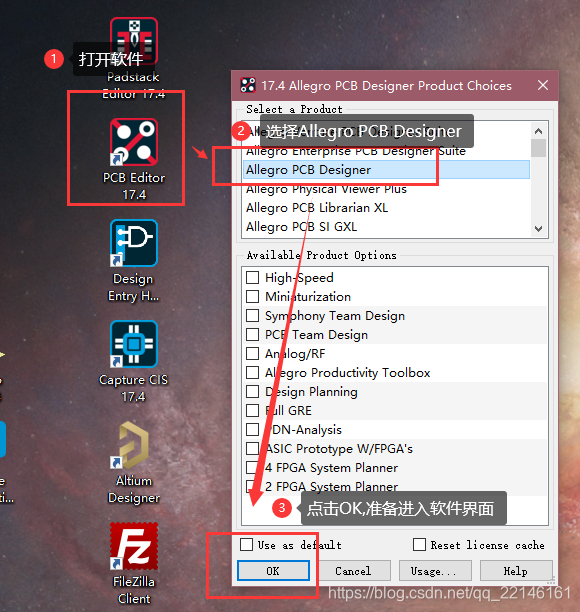

第一步:打开软件,点击图标,选择Allegro PCB Designer,点击OK.

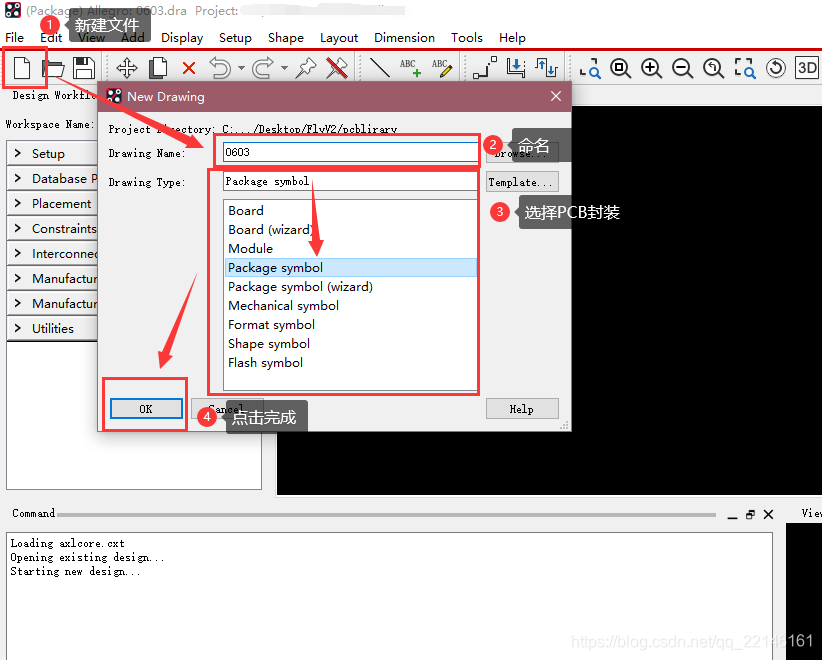

新建文件,起名字,选择PCB封装,也就是Package symbol,点击OK,然后保存,如下图,

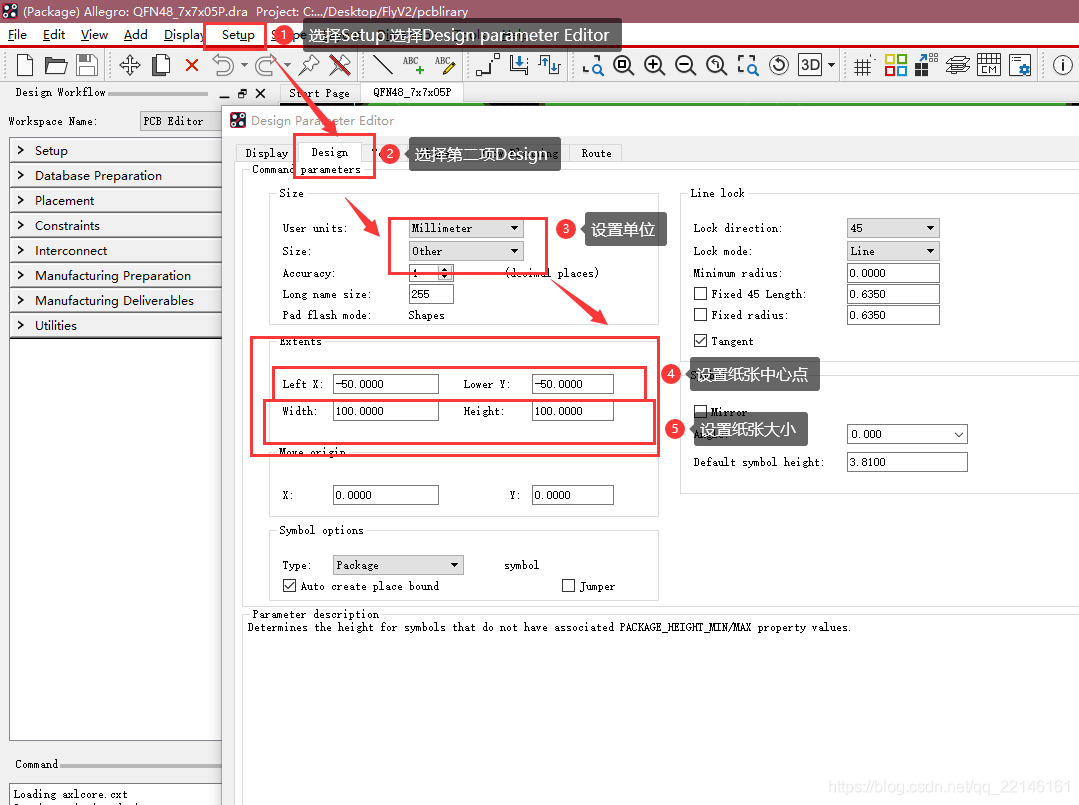

第二步:设置纸张大小,一些基本参数。点击软件上的“Setup”,选择第一项“Design Parameter Editor”(设计参数 编辑器 ).

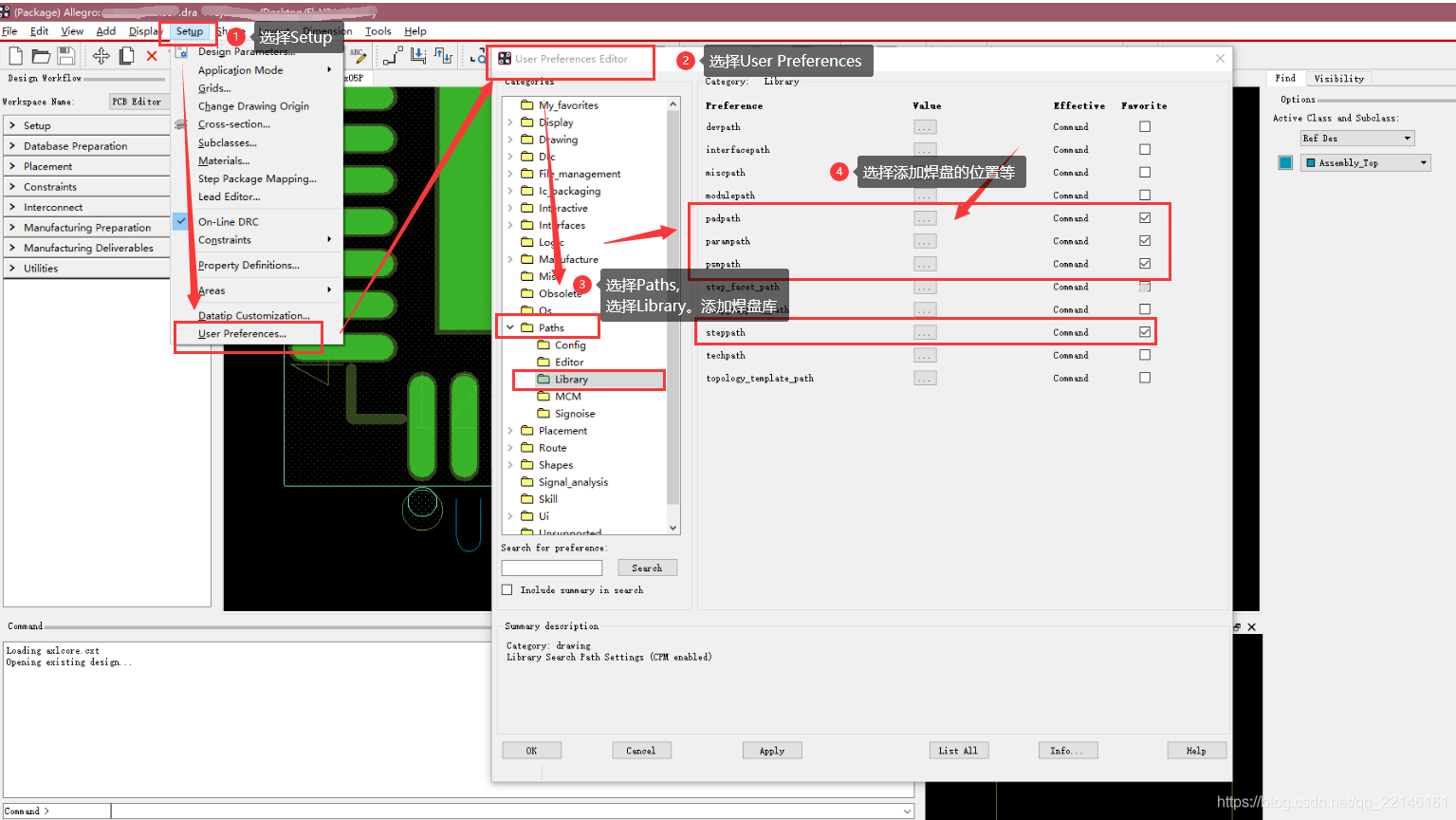

第三步:选择焊盘路径,依旧选择Setup 选择 User Preferences Editor ,选择 Paths(路径)。找到自己之前画焊盘的路径。

关于如何画焊盘请参考之前的文章:https://blog.csdn.net/qq_22146161/article/details/117093809

从这部开始可以进行真正的绘制部分了。

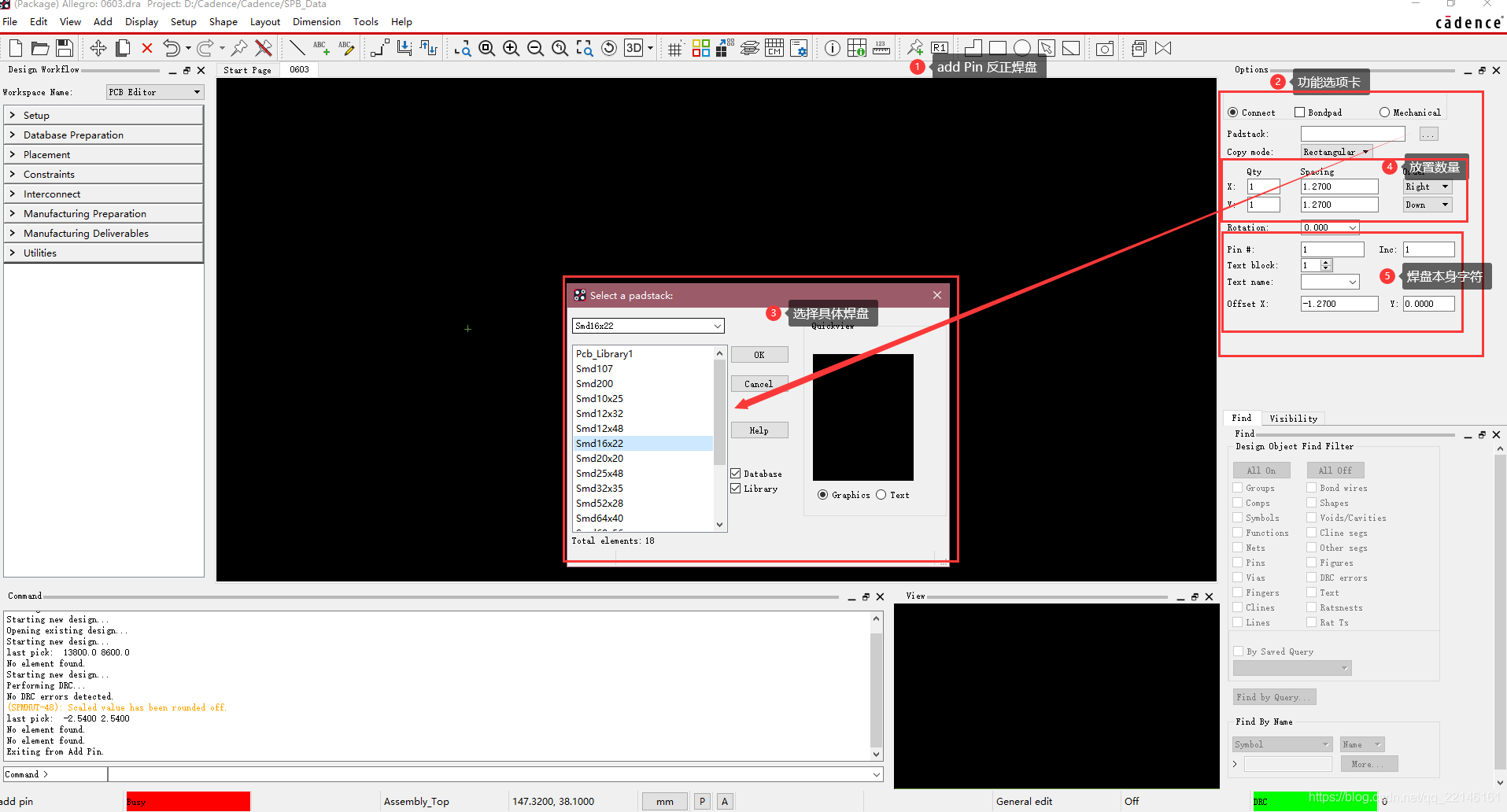

第4步:使用add Pin (添加焊盘)功能增加焊盘,通过Options功能选项卡,可以进行多种功能选择,选择合适的焊盘焊盘后,可以选择焊盘数量,就可以防止。

也可以通过Layout 》》Pins,调出焊盘界面。

第5步:

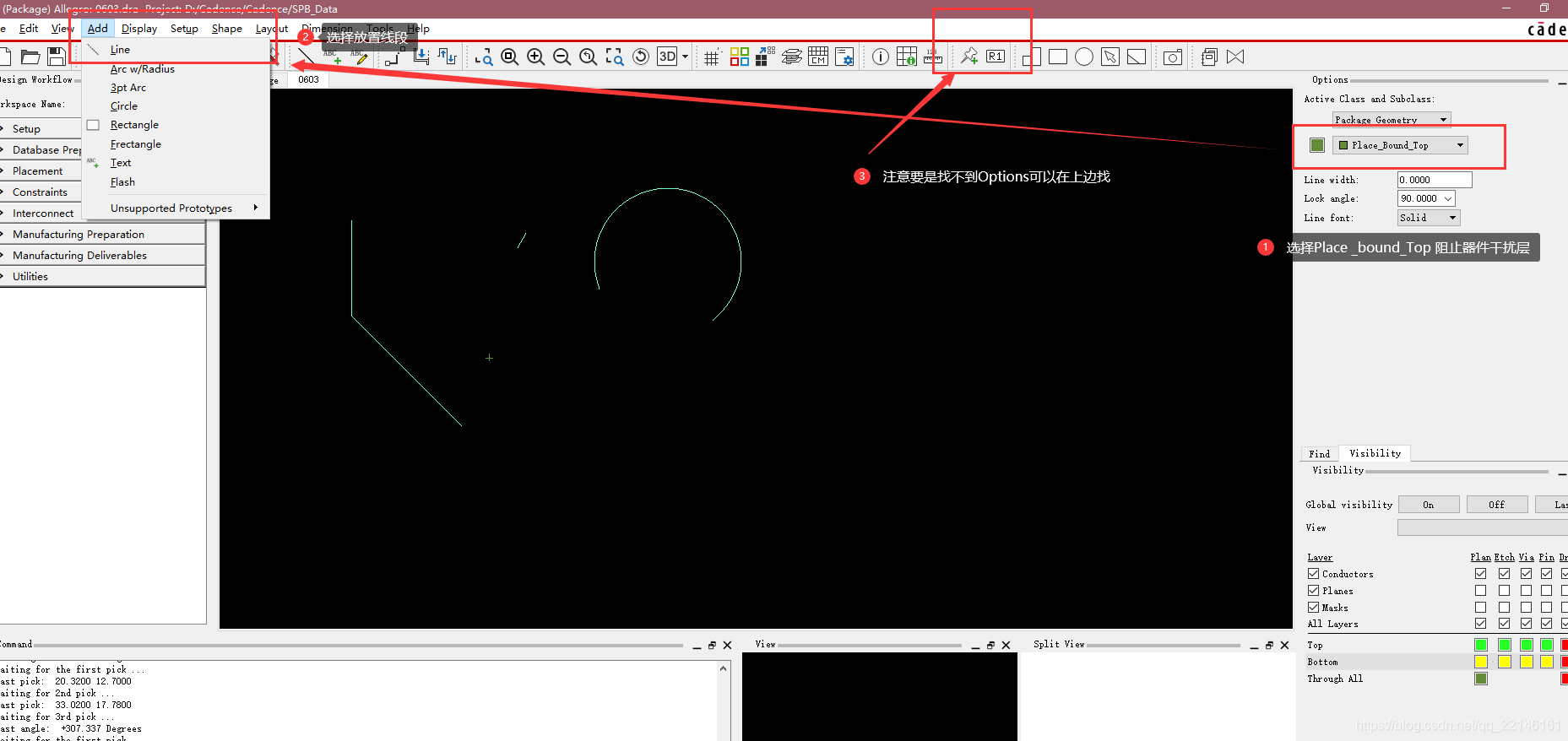

(1)设置Place_Bound_top(放置顶层边界):在Package Geometry 大类下,选择Place_Bound_top,器件之间的边界,阻止重叠,选好层后,点击Add,,然后选择。

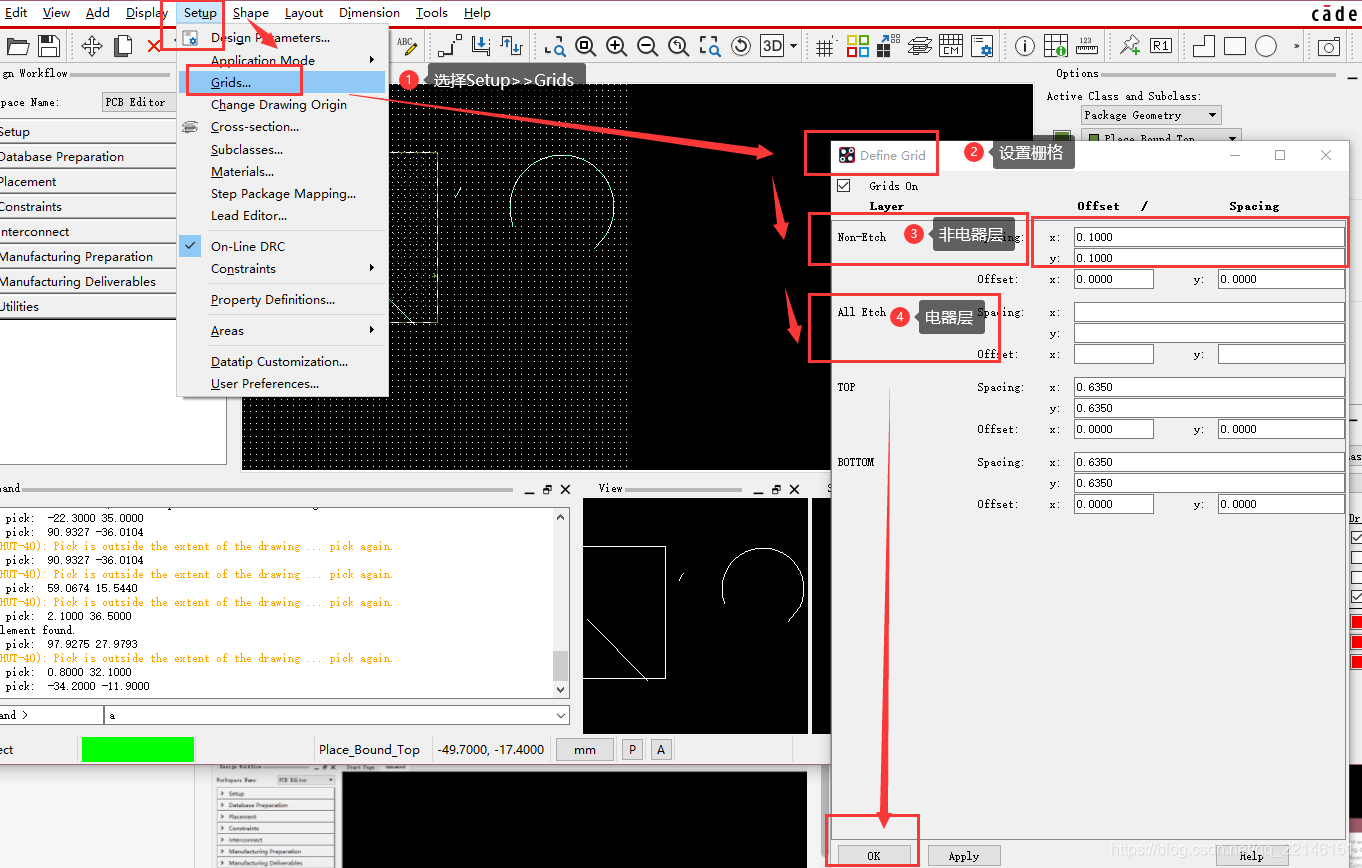

当觉得栅格位置不好掌控是,可以设置辅助栅格,就像原理图内部一样,设置网格,帮助画线。在setup>>Grids下设置。

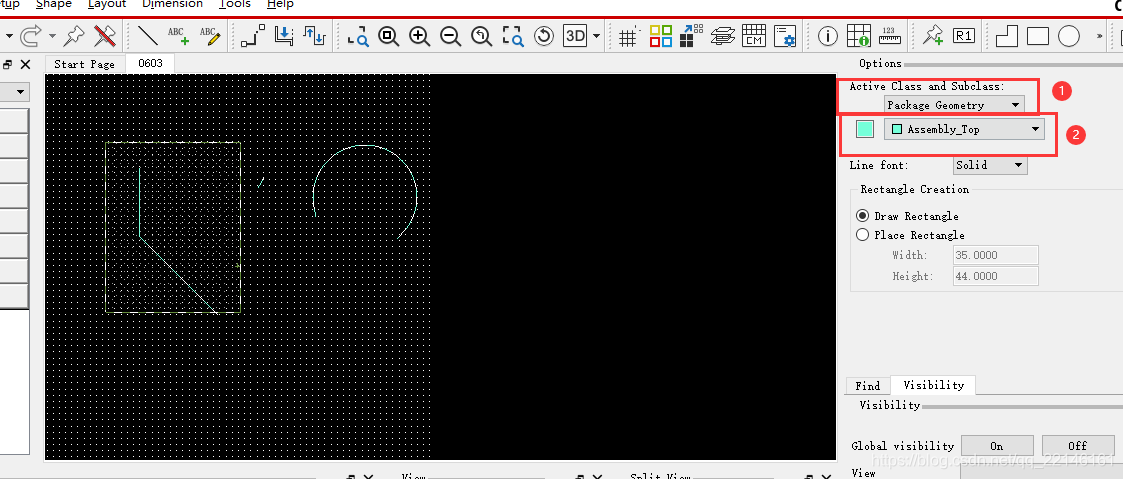

(2)设置Assemble_Top(装配顶层),如下图,放好Done.

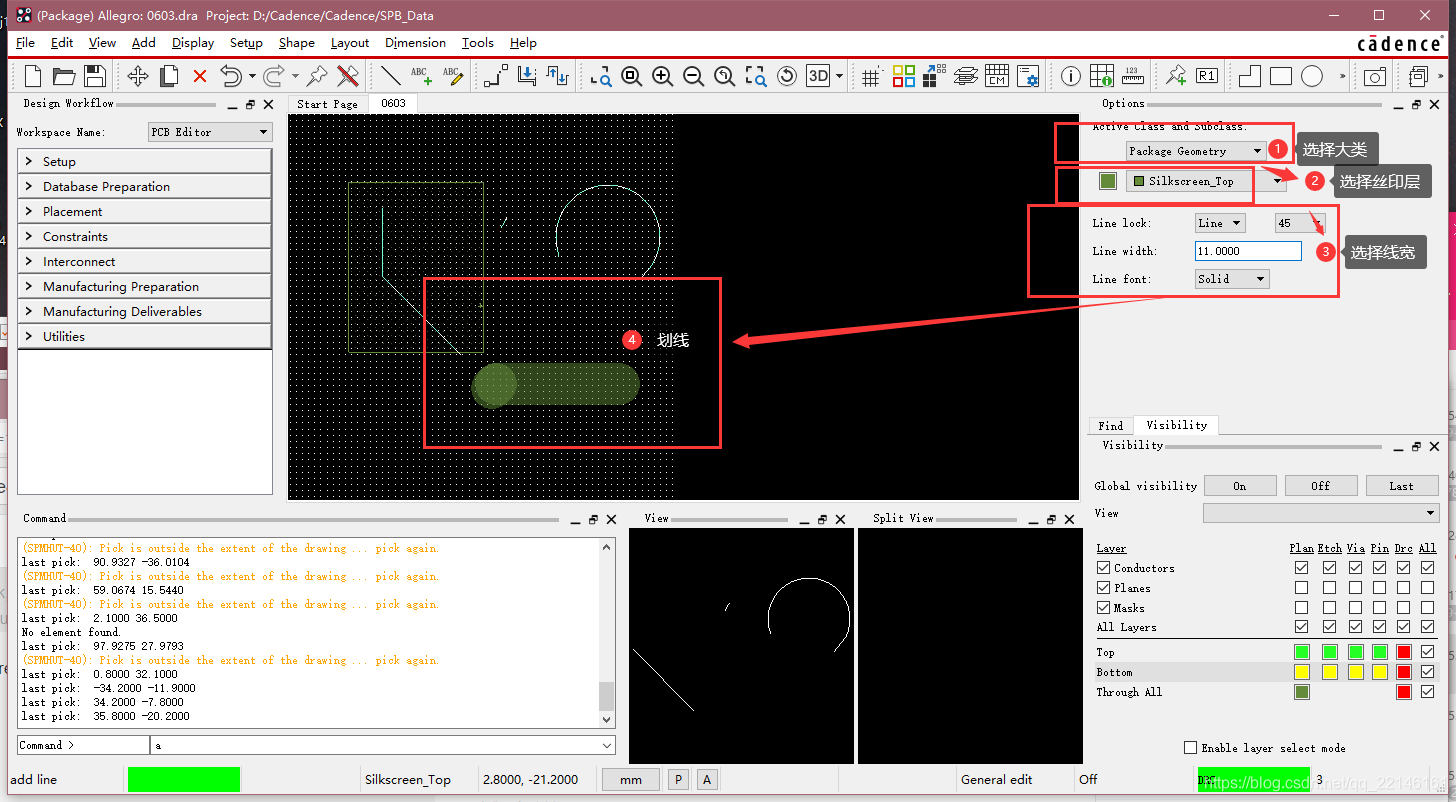

(3)放置丝印层得线Silksscreen_Top(丝印顶层):也在Package Geometry大类下,选择silkscreen_Top.

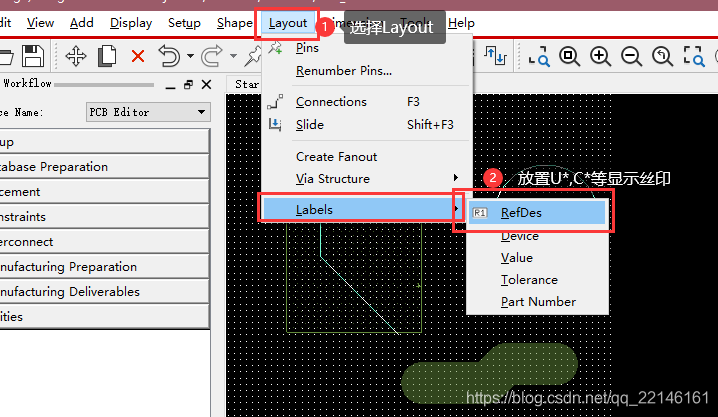

(4)标注器件命名使用,如下图,选择Layout>>Labels>>RefDes.我们画得的板子上,某个电容可能叫"C1"或者“C2”,某个芯片丝印有“U1”或者其他的,这步就是放置这个命名的。

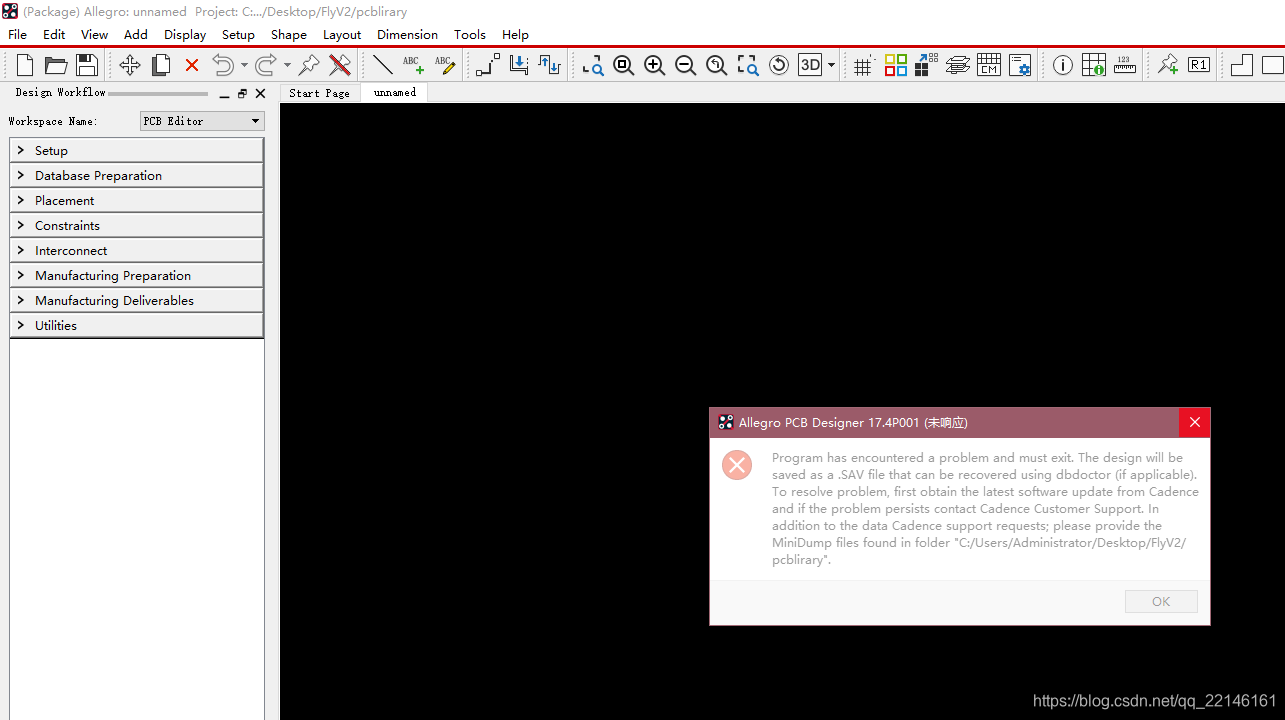

(1)有个错误,在新建文件的时候,出现的这个问题。更新补丁,使用

“吴川斌candece”对应版本补丁。更新后就解决这个问题。

免责声明:本文系网络转载或改编,未找到原创作者,版权归原作者所有。如涉及版权,请联系删