软件

产品

既然做了过孔,就要用。而且打算用过孔代替埋孔,盲孔,要看到效果。本篇就来实验一下:

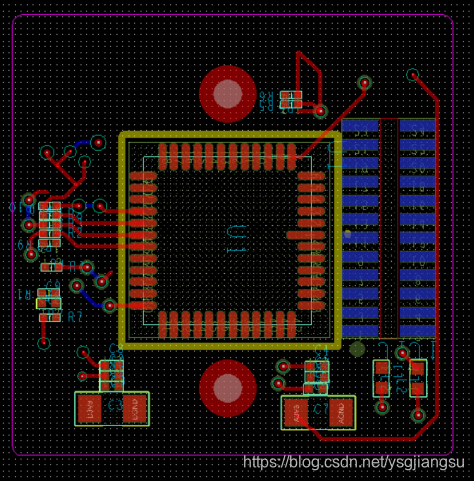

首先,PCB分层(见Cadence软件使用记录5)

啰嗦几句:分层之后,分别是TOP - GND - PWR - BOT ,中间两层是平面,采用负片设计。

开始了:

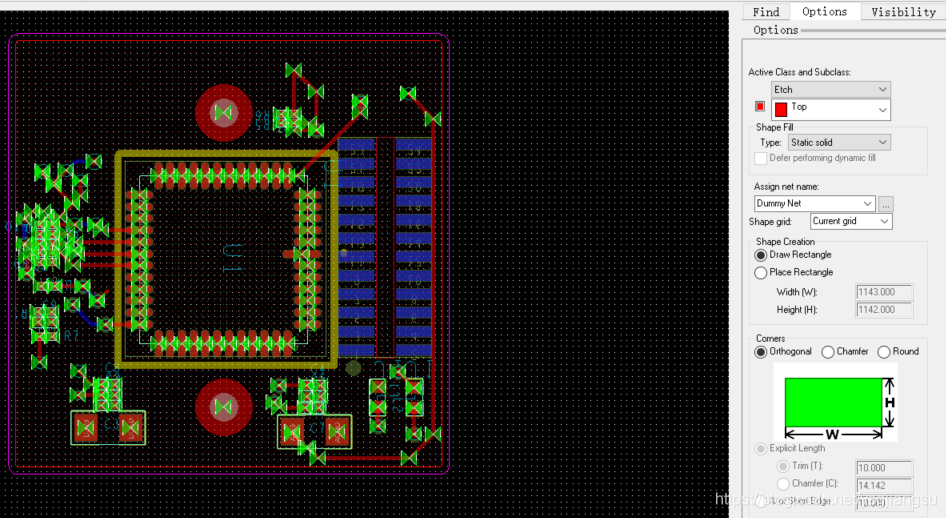

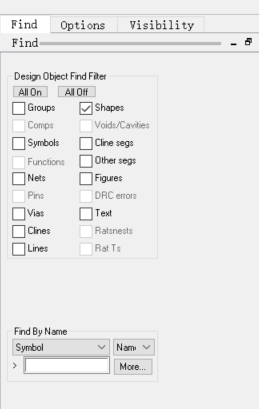

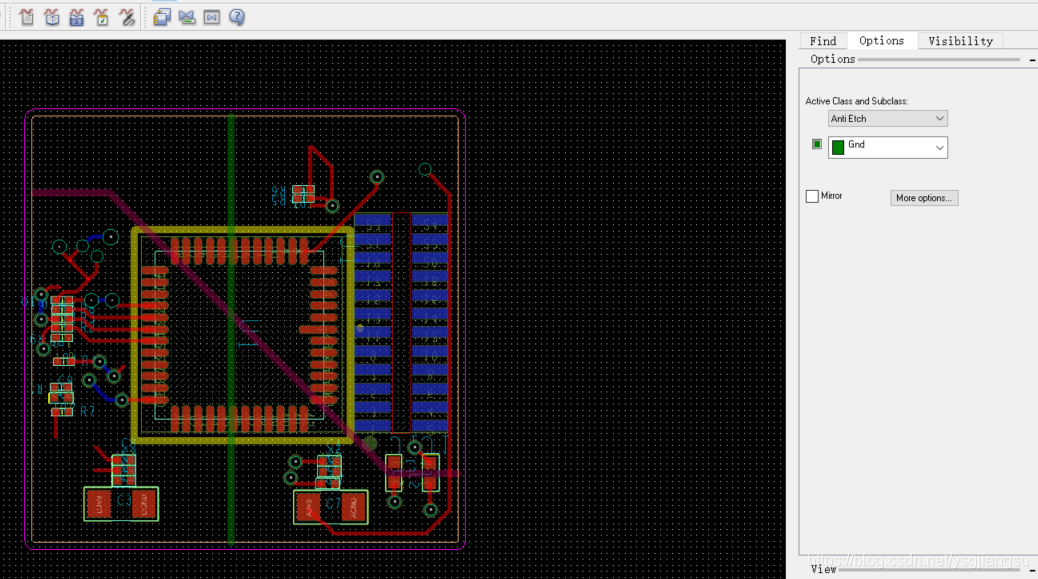

先分别在中间两层,划一块anti etch区域,这个区域就是一个大平面。(与AD不一样,AD认为你把我定义成internal plane了,那我就是plane了,自动帮你画好大平面,而cadence需要你自己先画一个。这里特地再申明一下,新版cadence已经不需要这么设置了,画好route keepin,再添加 分割 线就能分割,下文会讲)

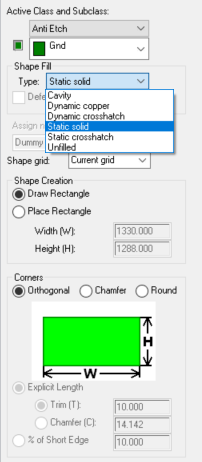

| 类型 | 释义 |

|---|---|

| Cavity | 内嵌凹槽(我也没用过) |

| dynamic copper | 动态铜 |

| dynamic crosshatch | 动态网状铜 |

| static solid | 静态铜 |

| static crosshatch | 静态网状铜 |

| unfilled | 不填充 |

因此,我们选择动态铜

直接画线就行,注意是在anti etch层,因为是负片。建议分割线粗一些,压差越大越粗。

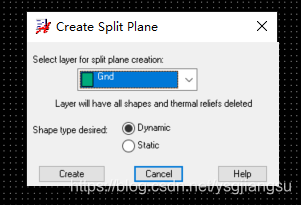

Edit->splite plane->create

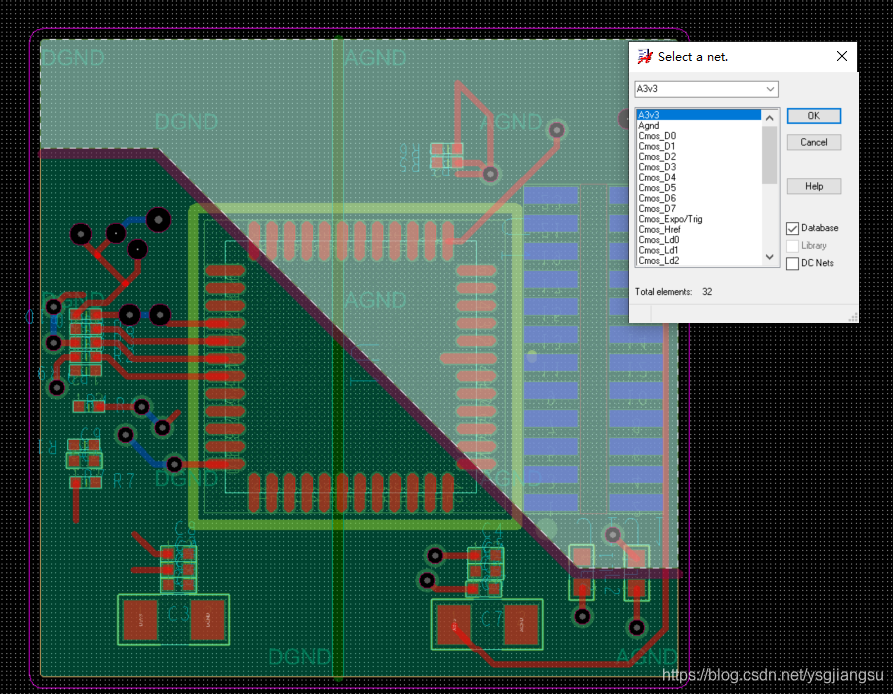

依次 赋值 就好了

这里说一下,有不少人建议新手都用正片设计,可以省去flash设计。我觉得非常不好!路迟早要走的,要弄明白为什么才能理解更深刻,才能设计的更好。

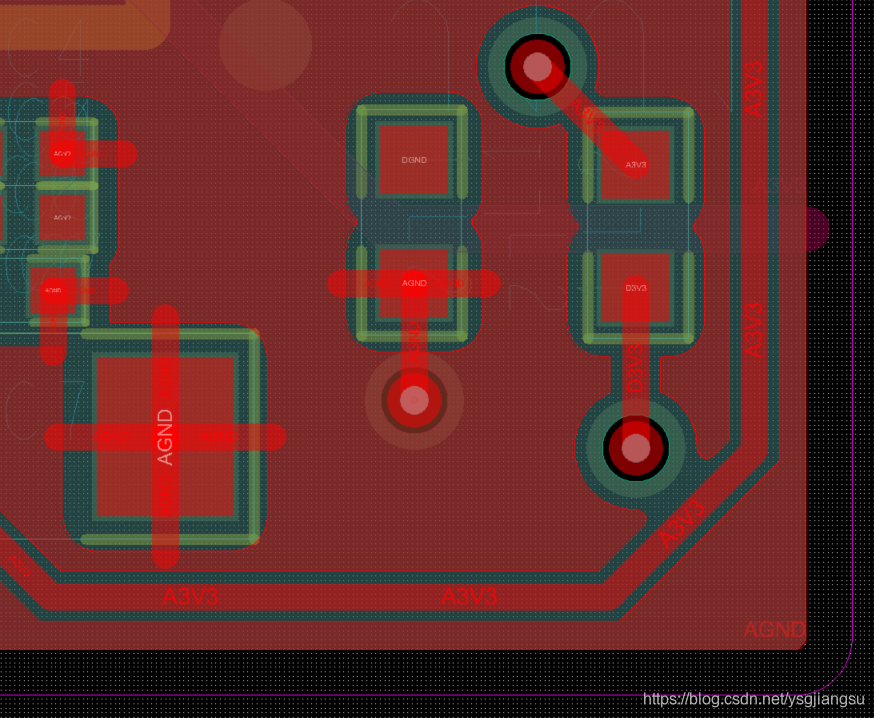

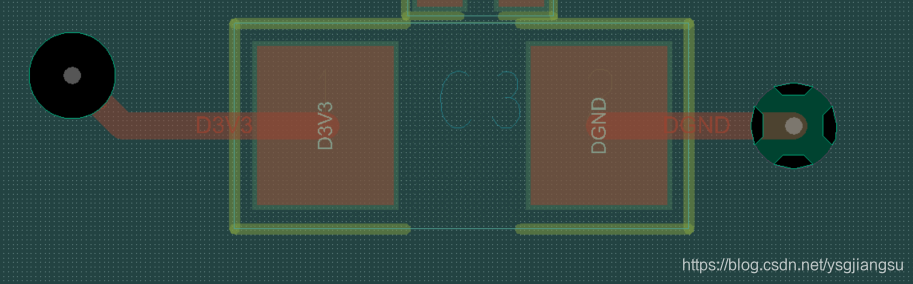

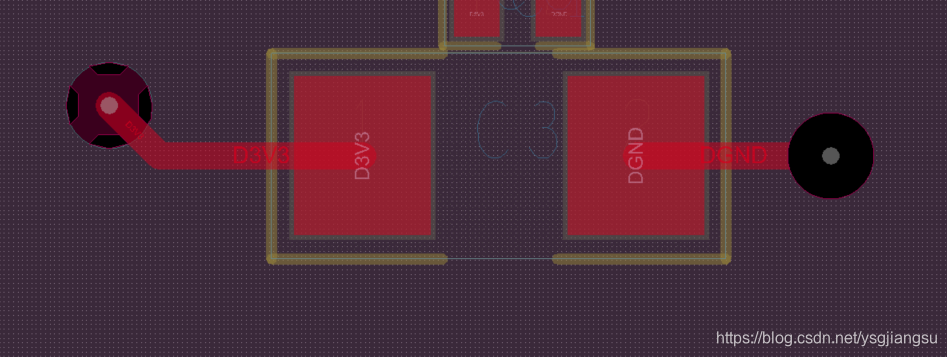

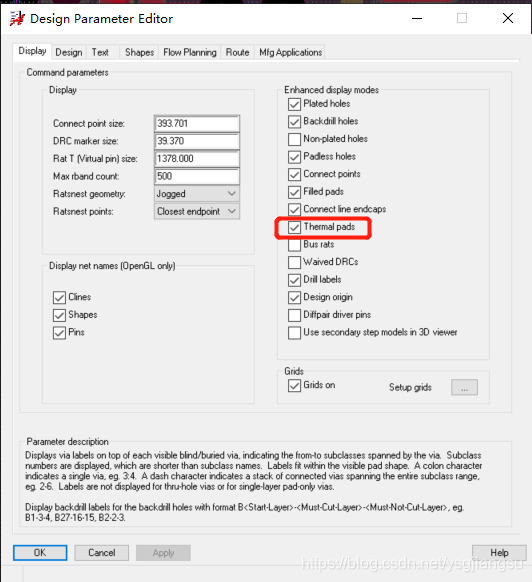

有的朋友可能怎么切换图层,都看不到flash花型,如果确实是按照之前的流程做的,那有可能是显示 控制 的问题:

勾选Thermal Pad就好了