软件

产品

allegro 设置出线方向

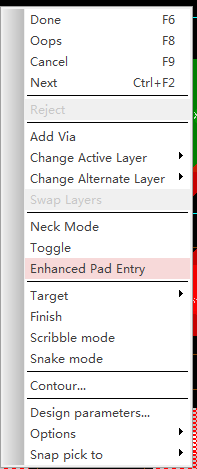

鼠标右键,取消enhanced pad entry

先直后斜取消选择toggle,反之则是先斜后直(下图均为从左开始走线)

选择finish,会自动走完该段线

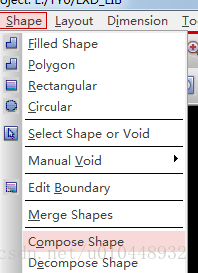

allegro 如何删除没有网络的net和shape

先锁定所有有网络的线和shape,然后再点击删除

在Allegro中如何Rename的时候把部分器件保护起来

把要重新Rename位号的器件在Edit – Properties中添加一个Auto_rename属性,记住右边的Find栏中要选择Comps

导入DXF文件时报错

'LINE' object may not exist on class 'ROUTE KEEPOUT'解决 方法:先导入到outline层,然后再导入route keepout

在等长走线时,如何更改target目标线?

答:绕等长有两种:一种是设在一定范围内绕没有基准,就是说在一组 BUS 里必须绕到这个范围内才会变绿,这个我一般不用,因为BUS里少绕一根不到这个范围就不会变绿。另一种就是设在一定范围内有基准的,也许就是你表达的这种,ElectricalConstraint Set-->Net-->Routing-->Relative Propagation-->relative Delay-->Delta:Tolerance下你想设做基准的Net,点鼠标右键,在 下拉菜单 选择set as target。

Allegro 常用Properties

| Property | 可加入之对象 | 可否在线路图中加入 |

| ALT_SYMBOLS | Device | yes |

| AUTO_GENERATED_TERM | Component | no |

| AUTO_RENAME | Reference Designator (Component) | no |

| BOARD_THICKNESS | Board | no |

| BOM_IGNORE | Component | yes |

| BUS_NAME | Net | yes |

| CLIP_DRAW | Design (board), Symbol | no |

| CLIP_DRAWING | Connect line, Device, Pin, Filled rectangle, Line, Rectangle, Shape, Symbol, Via, Void | no |

| CLOCK_NET | Net | yes |

| COMPONENT_WEIGHT | Reference Designator (Component) | yes |

| C_TEMPERATURE | Reference Designator (Component) | yes |

| DENSE_COMPONENT | Reference Designator (Component) | yes |

| DFA_DEV_CLASS | Board, Symbol | no |

| DIFFERENTIAL_PAIR | Net | yes |

| DIFFP_2ND_LENGTH | Net | no |

| DIFFP_LENGTH_TOL | Net | no |

| DRIVER_TERM_VAL | Net | no |

| ECL | Net | yes |

| ECL_TEMP | Net | yes |

| EDGE_SENS | Net, Xnet, ECSet | no |

| ELECTRICAL_CONSTRAINT_SET | Net | yes |

| FILLET | Connect Line | no |

| FIRST_INCIDENT | Net, Xnet, ECSet | no |

| FIX_ALL | Reference Designator (Component) | yes |

| FIXED | Reference Designator (Component), Symbol, Connect Line, Filled rectangle, Line, Net, Pin, Rectangle, Shape, Via | yes |

| FIXED_T_TOLERANCE | TPoint | no |

| FP_BOARD_CLEARANCE | Board | no |

| FP_NOTES_TEXT_BLOCK | Board | no |

| FP_REFDES_TEXT_BLOCK | Board | no |

| FP_ROOM_NAME_TEXT_BLOCK | Board | no |

| GROUP | Function Designator | yes |

| HARD_LOCATION | Reference Designator, Function Designator | yes, but not seen in schematic as LOCATION |

| HEAT_SINK_FACTOR | Reference Designator (Component) | yes |

| IDF_OWNER | All Objects | no |

| IMPEDANCE_RULE | Net, ECSet | no |

| INSERTION_CODE | Device | yes |

| J_TEMPERATURE | Reference Designator (Component) | yes |

| LEAD_DIAMETER | Board, Symbol | no |

| LOAD_TERM_VAL | Net | no |

| LOGICAL_PATH | Function Designator (Component) | yes, but assigned by PXL. Not user defined. |

| MAX_BOND_LENGTH | Net, Connect Line | no |

| MAX_BVIA_STAGGER | Net | no |

| MAX_EXPOSED_LENGTH | Net, ECSet | yes |

| MAX_FINAL_SETTLE | Net, ECSet | yes |

| MAX_OVERSHOOT | Net, ECSet | yes |

| MAX_PARALLEL (PARALLELISM) | Net, Connect Line, ECSet | no |

| MAX_PEAK_XTALK (MAX_PEAK_CROSSTALK) | Net | no |

| MAX_POWER_DISS | Device, Reference Designator (Component) | yes |

| MAX_SSN | Net | no |

| MAX_STUB_LENGTH | yes | |

| MAX_UNDERSHOOT | Net, Connect Line | yes |

| MAX_VIA_COUNT | Net, ECSet | yes |

| MAX_XTALK (MAX_CROSSTALK) | Net | no |

| MAX_XTALK (MAX_CROSSTALK) | Net, Connect Line | no |

| MIN_BVIA_GAP | Net | no |

| MIN_BVIA_STAGGER | Net | no |

| MIN_FIRST_SWITCH | Net, ECSet | no |

| MIN_HOLD | Net, Pin | yes |

| MIN_LINE_WIDTH | Net, Connect Line | yes |

| MIN_NECK_WIDTH | Net, Connect Line | yes |

| MIN_NOISE_MARGIN | Net, ECSet | yes |

| MIN_SETUP | Net, Pin | yes |

| NET_PHYSICAL_TYPE | Net, Constraint Area (Shape, Rectangle) | yes |

| NET_SCHEDULE | Net, ECSet | no |

| NET_SPACING_TYPE | Net, Constraint Area (Shape, Rectangle) | yes |

| NO_DRC | Pin, Via | no |

| NO_GLOSS | Net | yes |

| NO_LIN2SHAPE_FAT | Connect Line | no |

| NO_PIN_ESCAPE | Reference Designator (Component) , Net, Pin | yes |

| NO_RAT | Net | yes |

| NO_RIPUP | Net | yes |

| NO_ROUTE | Reference Designator (Component), Net | yes |

| NO_SHAPE_CONNECT | Pin, Via | yes |

| NO_SWAP_GATE | Reference Designator, Function Designator | yes, but assigned by PXL. See PXL documentation. |

| NO_SWAP_GATE_EXT | Function Designator | yes, but assigned by PXL. See PXL documentation. |

| NO_SWAP_PIN | Reference Designator, Function Designator, Pin | yes, but assigned by PXL. See PXL documentation. |

| NO_TEST | Net | yes |

| NO_VIA_CONNECT | Pins, Vias | no |

| PACKAGE_HEIGHT_MAX and PACKAGE_HEIGHT_MIN | Rectangle, Shape | no |

| PARALLELISM (MAX_PARALLEL) | Connect Line, Net | no |

| PIN_ESCAPE | Reference Designator, Pin | yes |

| PIN_SIGNAL_MODEL | Pin | no |

| PINUSE | Pin | yes, but assigned by PXL. See PXL documentation. |

| PLACE_TAG | Reference Designator (Component) | no |

| PLATING | Shape | no |

| PROBE_NUMBER | Net | yes |

| PROPAGATION_DELAY | Net, ECSet | no |

| PULSE_PARAM | Net, Xnet, Bus, Diff Pair | no |

| RATED_CURRENT | Device | yes |

| RATED_MAX_TEMP | Device | yes |

| RATED_POWER | Device | yes |

| RATED_VOLTAGE | Device | yes |

| RATSNEST_ SCHEDULE | Net, ECSet | no |

| REF_DES_FOR_ASSIGN | Function | no |

| RELATIVE_PROPAGATION_DELAY | Net, ECSet | no |

| REUSE_ID | Compnent, Symbol | |

| REUSE_INSTANCE | Component | yes |

| REUSE_MODULE | Component | yes |

| REUSE_NAME | Component | yes |

| REUSE_PID | Component, Symbol | |

| ROOM | Reference Designator, Function Designator | yes |

| ROOM_TYPE | Room Boundary | no |

| ROUTE_PRIORITY | Net | yes |

| ROUTE_TO_SHAPE | Net | no |

| SAME_NET | Nets | no |

| SHIELD_NET | Net | yes |

| SHIELD_TYPE | Net | yes |

| SLOTNAME | Function | no |

| STUB_LENGTH | Net, ECSet | yes |

| SWAP_GROUP | Function Designator | yes, but assigned by PXL. not user-assigned. |

| SYS_CONFIG_NAME | Board | no |

| T_TEMPERATURE | Reference Designator (Component) | yes |

| TERMINATOR_PACK | Device | no |

| TESTER_GUARDBAND | Net, Pin | no |

| THERMAL_RELIEF | Thermal Connect Line | no |

| THICKNESS | Layout Cross Section | no |

| TIMING_DELAY_OVERRIDE | Net, Pin | no |

| TOL | Device | yes |

| TOPOLOGY TEMPLATE | Net | yes |

| TOPOLOGY_TEMPLATE_REVISION | Net, ECSet | yes |

| TOTAL_ETCH_LENGTH | Xnet, net, bus or diff pair | yes |

| TS_ALLOWED | Net | yes |

| UNFIXED_PINS | Board, Symbol | no |

| VALUE | Discrete Device | yes |

| VIA_LIST | Net | no |

| VOLTAGE | Reference Designator (Component) | yes |

| WEIGHT | Pin | no |

| WIRE_LENGTH | Net | yes |

| XTALK_ACTIVE_TIME | Net, ECSet | no |

| XTALK_IGNORE_ NETS | Net | no |

| XTALK_SENSITIVE_TIME | Net, ECSet | no |

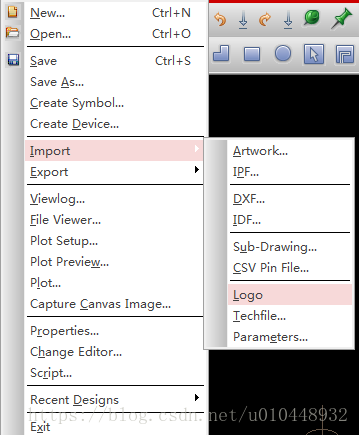

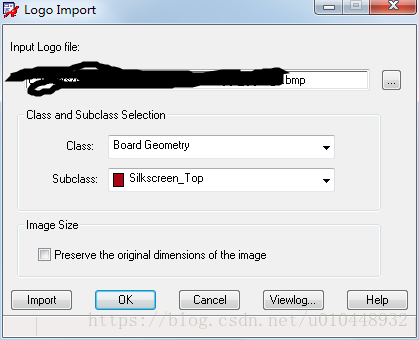

导入logo

打开封装编辑软件

免责声明:本文系网络转载或改编,未找到原创作者,版权归原作者所有。如涉及版权,请联系删