随着高速数字信号的速率不断提高, PCB 设计中需要对高速数字信号的阻抗和串扰、 衰减等性能进行更加严格的控制, 通孔的无盘设计逐渐成为高速数字 PCB 设计 和制造中的一个必要措施。

无盘设计指的在PCB设计时,去除非功能焊盘(non-functional pads ),即通孔焊盘(Through Pin)或过孔(Via)在不连接层的焊环。通常情况下是删除PCB内层的非功能焊盘。

(1) 非功能能焊盘在低速电路中对信号阻抗和传输损耗影响不大, 但是在高速数字电路中, 会带来额外的损耗,会影响高速数字信号的阻抗一致性,所以必须想办法在设计中减少非功能焊盘的不利影响, 否则带来的反射和插损过大, 信号质量将不符合标准规范要求, 给公司的产品质量带来隐患。

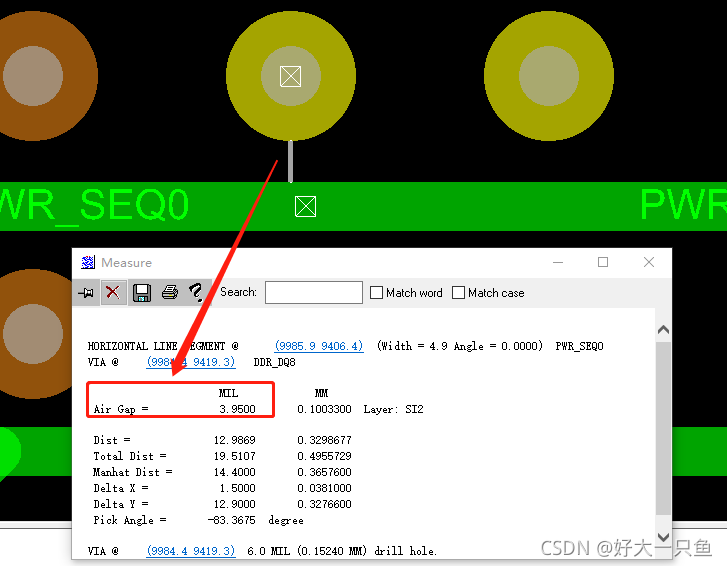

(2) 此外, 随着芯片封装技术的发展, 芯片的管脚间距也越来越小, 芯片内部的差分信号的出线空间经常不足,而采用无盘设计则可起到增加走线空间的作用, 满足工艺制造要求。 如下图,高速差分信号距离通孔的间距为 3. 95mil(约0.1mm ), 接近目前国内主流板厂的工艺极限, 如果采用这种设计, 板厂制造的实际产品良率会很低, 而且可靠性方面也存在很大的短路可能性。 因此必须采用去除通孔的非功能焊盘的设计, 既保证高速信号的信号质量, 也满足工艺制造能力, 不增加不必要的成本和风险。

图1

本文介绍 Allegro16.6 版本的无盘设计步骤:

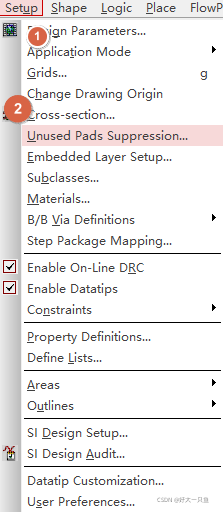

1、选择Setup→Unused Pads Suppression 命令, 弹出无盘设计窗口。

图2

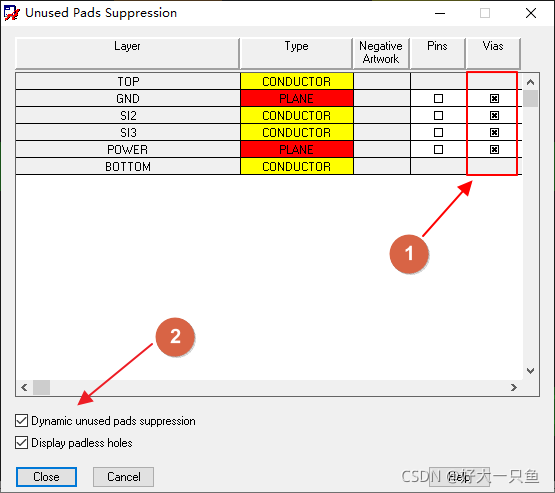

图3

2、如图3所示,该PCB为6层板,在无盘设计窗口中,TOP层和BOTTOM层是不能选择的,在后面两列中,可以选择Pins和Vias。如图3所示,对GND、SI2、SI3、POWER这4层的Vias选中进行无盘设计。 注意要勾选窗口 下面的 dynamic unused pads suppression 和 Display padless holes。 这样布线的时候软件会动态的识别设置了无盘设计的层面, 并且相应的无用焊盘也会显示不出来, 方面设计者随时掌握无盘设计的效果。

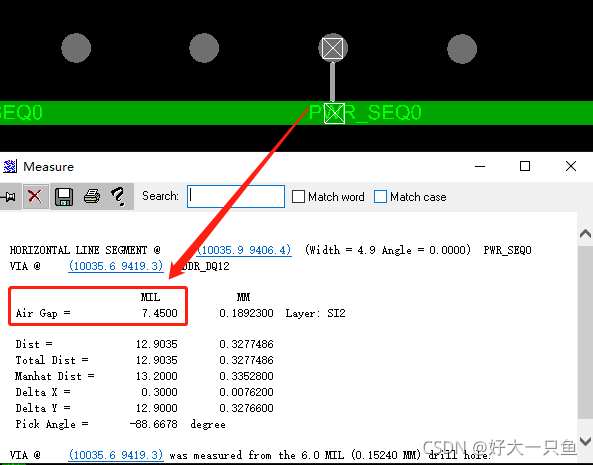

3、设置完成后,效果如图4所示,可以看到没有连接线层的通孔与走线的间距增加到7.45mil(即0.18923mm),大大增加了线与孔的间距,降低了PCB板的制造工艺,提升了良品率。

图4

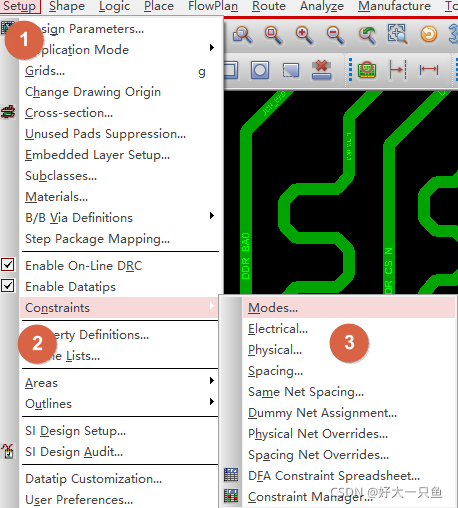

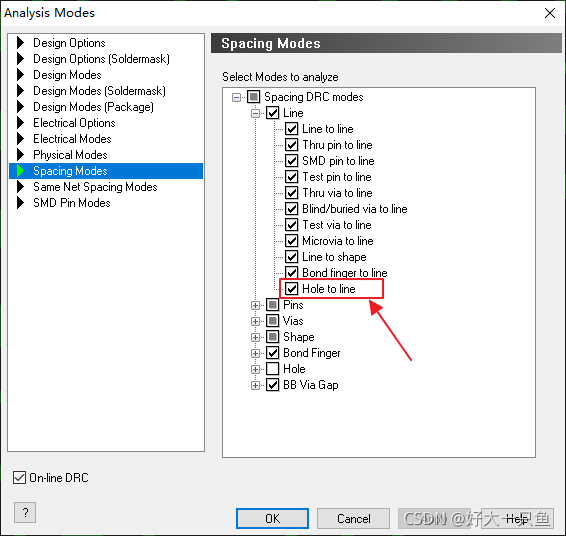

4、最后注意一点,需要在规则管理器中,确认打开Line到Hole的间距, 因为经过无盘设计后软件会在无盘的层把原来的通孔识别为 hole,因此需要把 Hole到其他元素的间距设置的大一些(如8mil甚至更大),如图5和图6所示。

图5

图6

免责声明:本文系网络转载或改编,未找到原创作者,版权归原作者所有。如涉及版权,请联系删