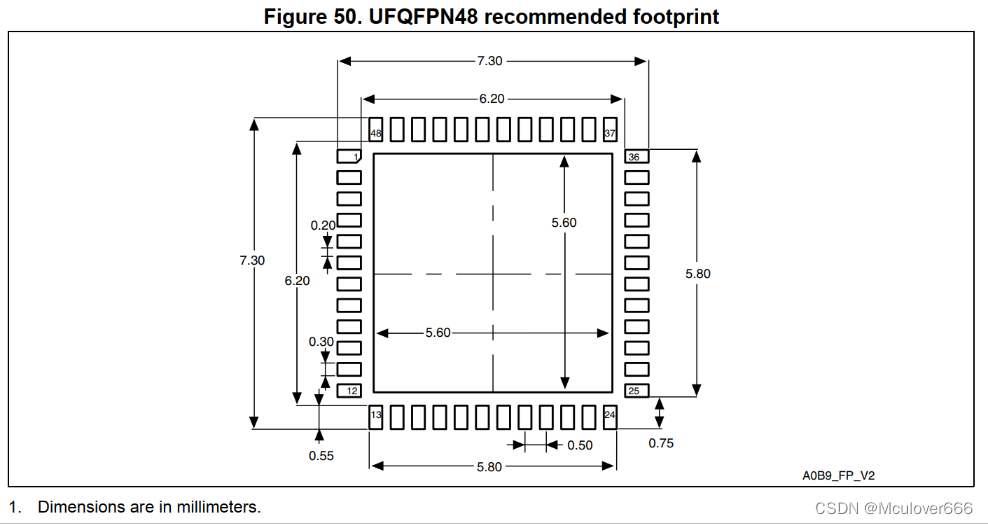

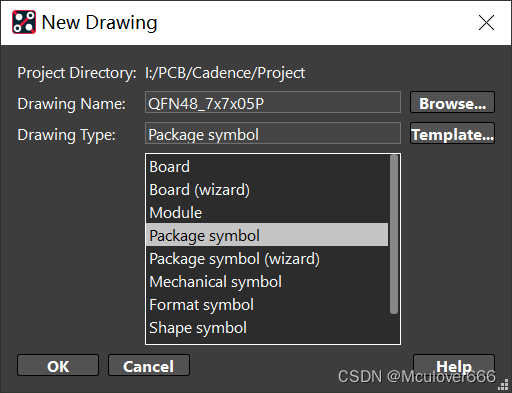

软件

产品

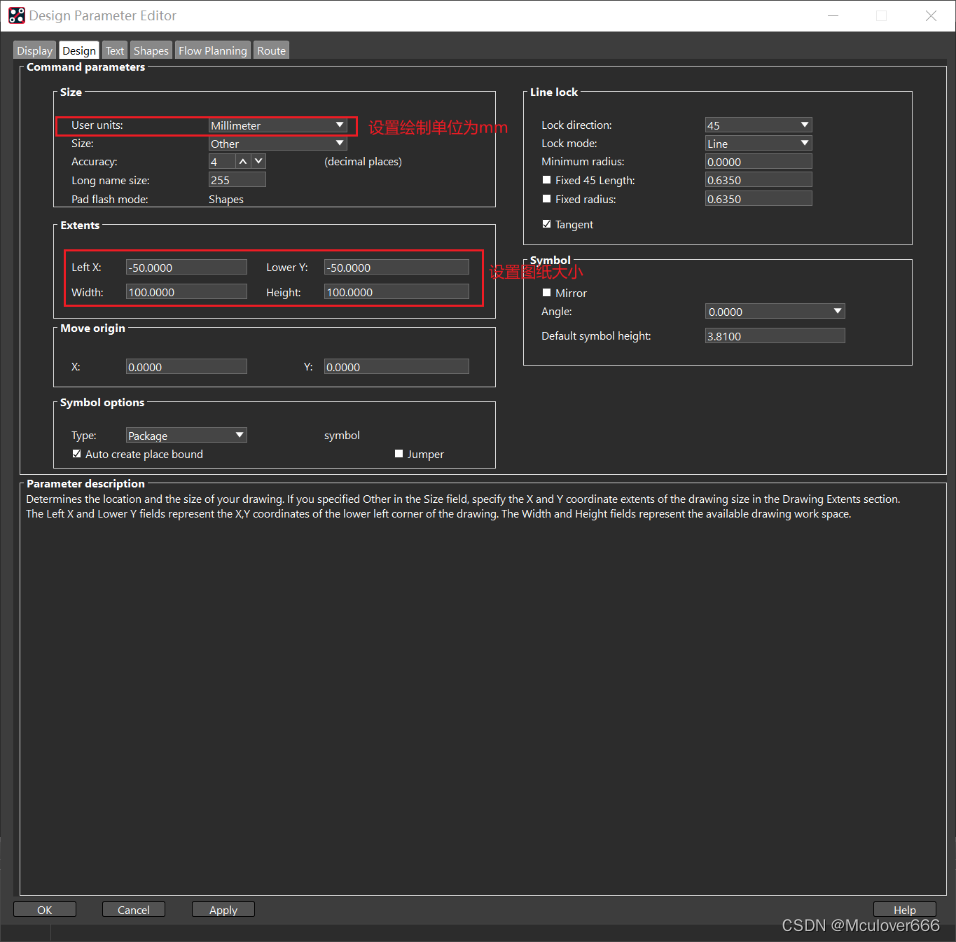

点击Setup->Design Parameter进行设置:

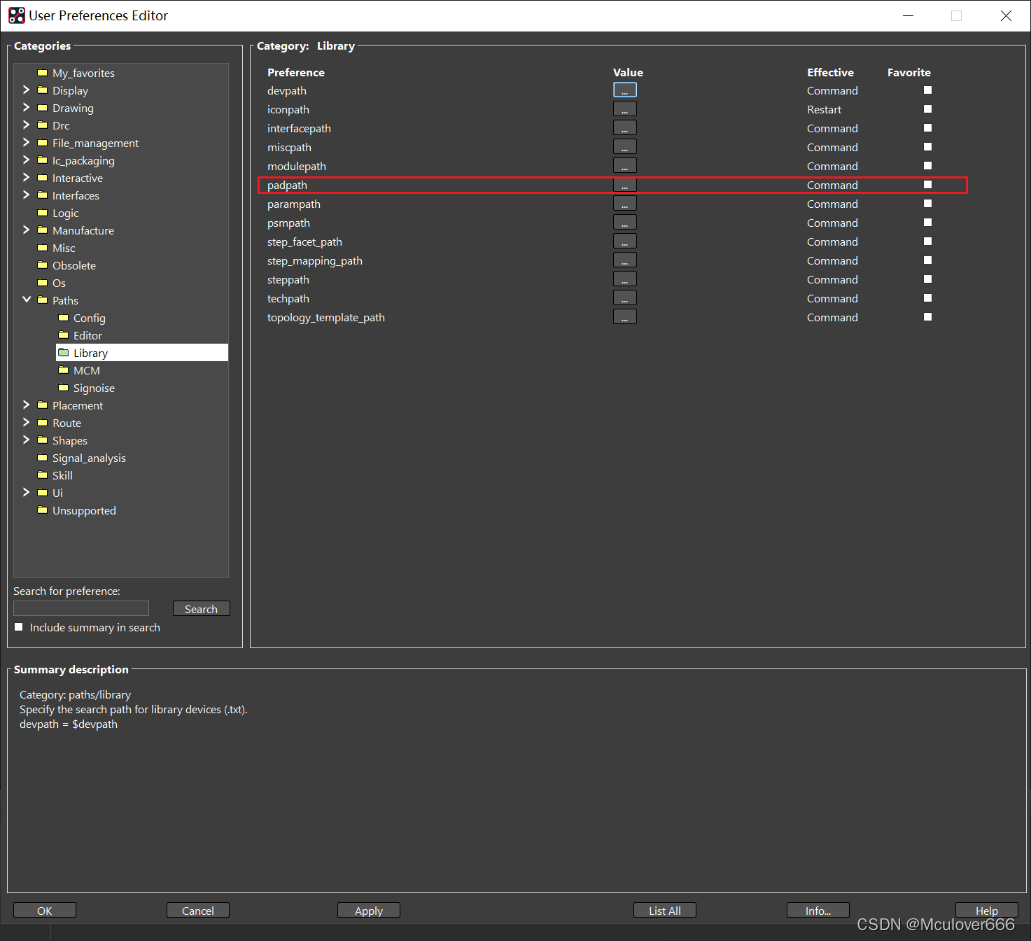

点击Steup->User Preferences:

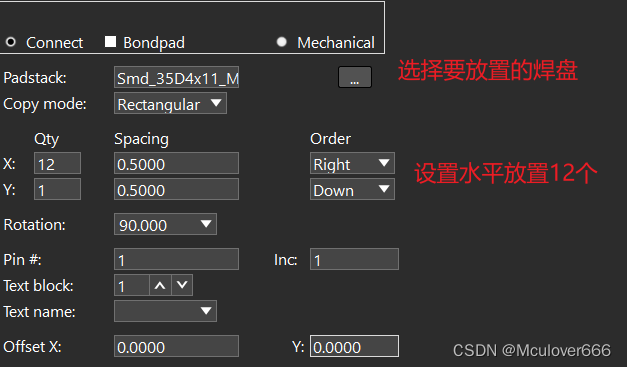

点击 Layout->Pins放置焊盘。

设置焊盘参数:

使用 命令 设置起始点:

x -2.75 y -3.7

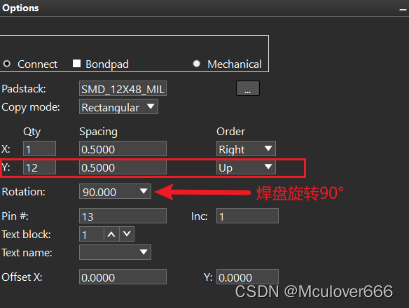

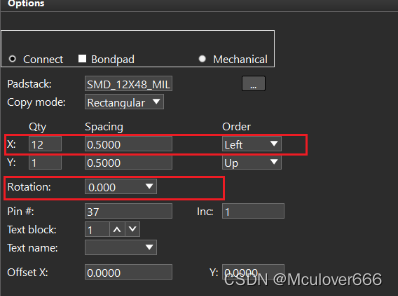

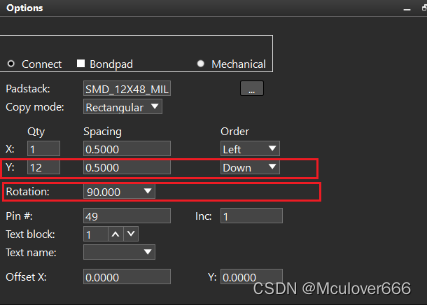

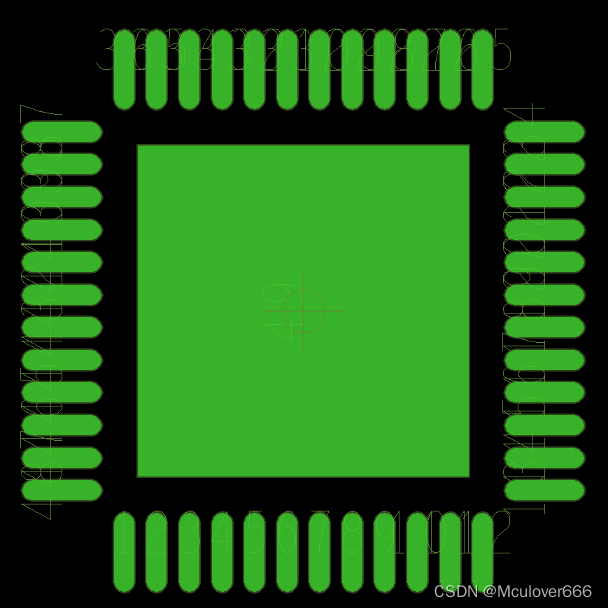

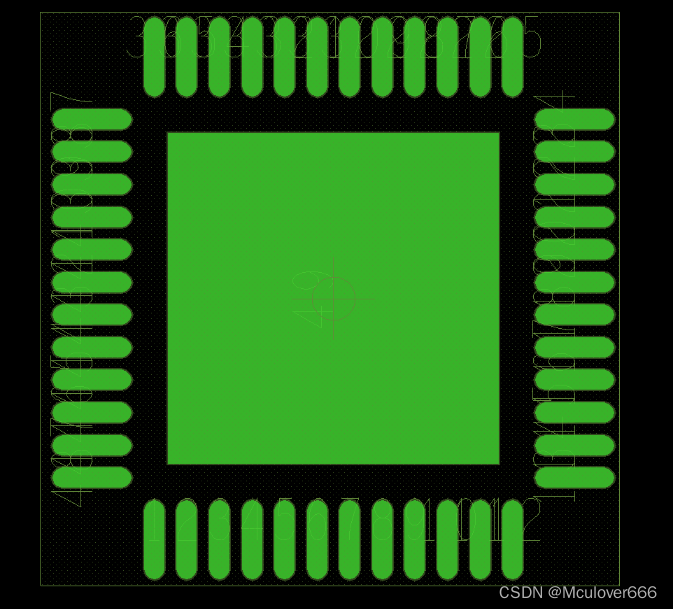

同样的方法放置其它三边:

x 3.7 y -2.75

x 2.75 y 3.7

x -3.7 y 2.75

最后放置中心焊盘:

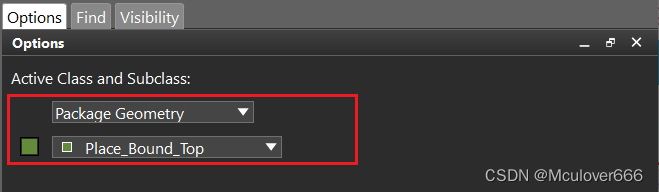

该层是表示器件的最大范围。

点击 Add-> Rectangle ,选择Subclass为Place Bound Top:

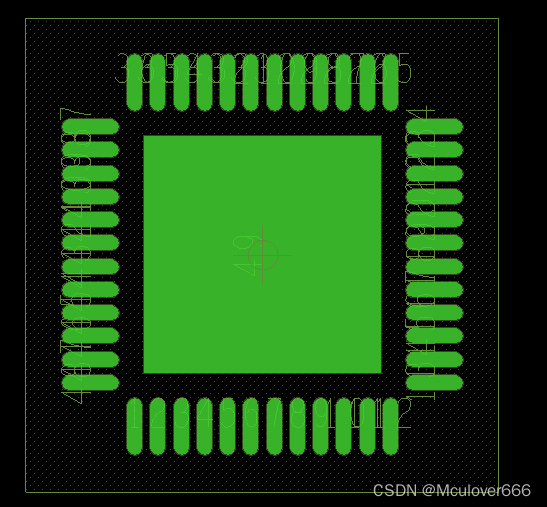

因为栅格的原因,放置出来的矩形太大了:

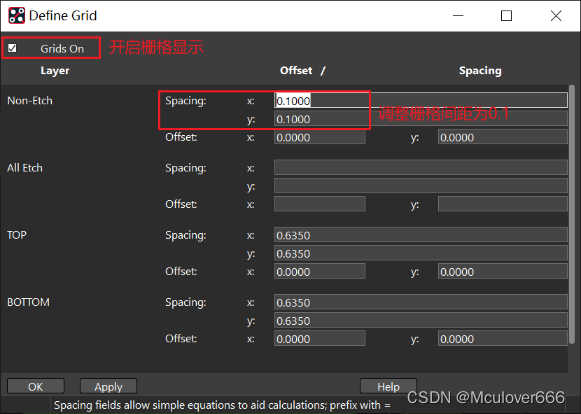

点击Setup -> Grid 调整栅格大小:

重新 绘制矩形 :

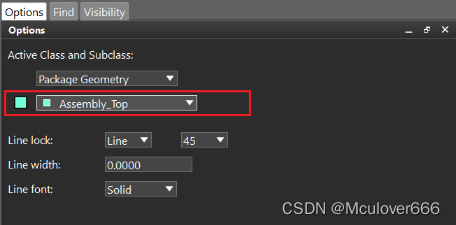

点击Add->Line,选择绘制在装配层Assembly_Top:

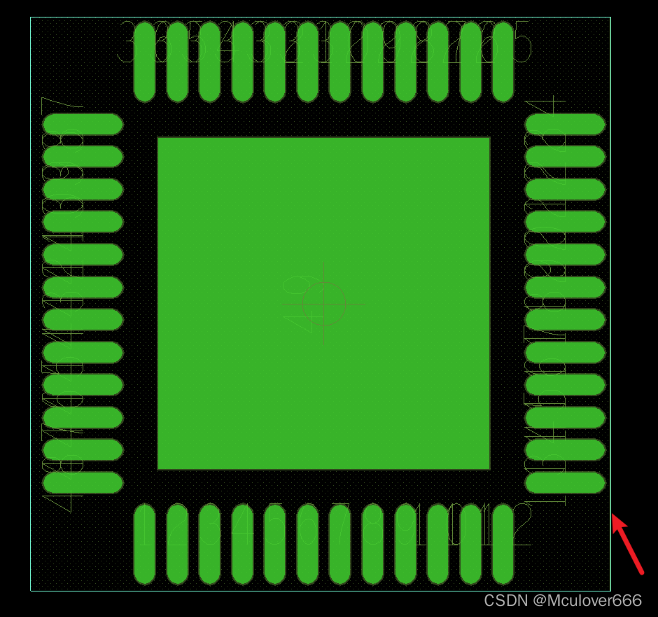

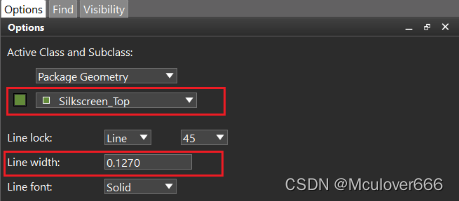

点击Add->Line,设置线宽为5mil(0.127mm):

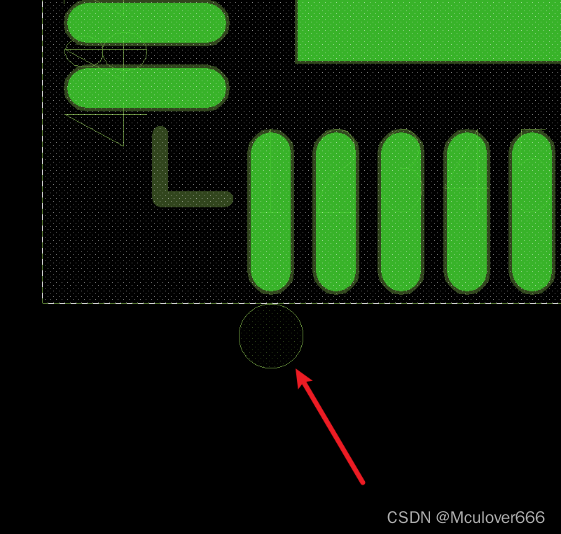

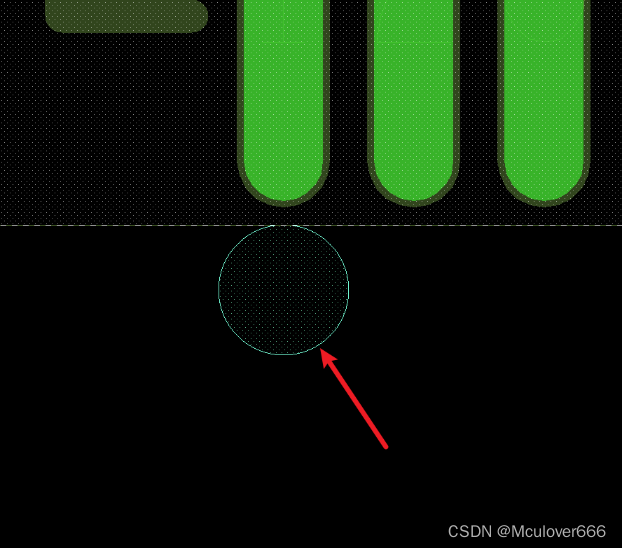

绘制1脚的小圆点,点击Add->Circle:

x -2.75 y -4.65

ix 0.25

以同样的方法,在装配层也画同样大小的一个圆:

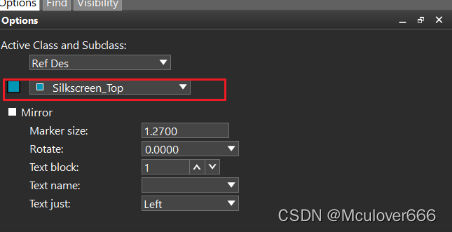

点击 Layout->Labels->RefDes,选择在丝印层放置:

点击要放置的位置,输入U*。

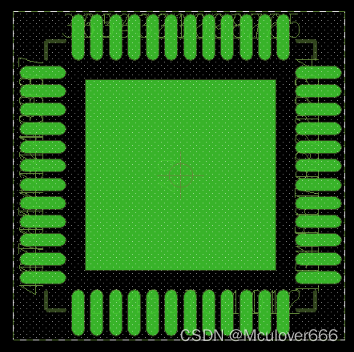

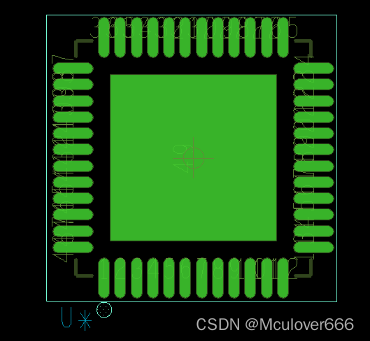

至此,STM32F411CEU6封装绘制完成:

免责声明:本文系网络转载或改编,未找到原创作者,版权归原作者所有。如涉及版权,请联系删