PCB初始化设计流程就需要导入结构图纸和原理图产生的网表。导入网表的原因是PCB上的走线和元件的逻辑关系是由原理图来决定的,因此PCB要将原理图产生的网表做为输入条件,参考原理图上的要求进行设计。

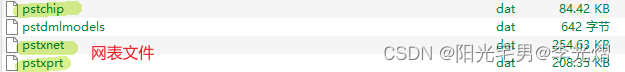

原理图通过网表与PCB产生关联,在星球文章:【原理图专题】OrCAD Capture常用文件扩展名 中我们给出 xxx.DAT就是OrCAD 产生的网表文件,网表文件可以将原理图中的逻辑关系和关键参数导入PCB设计中。Allegro可以支持OrCAD网表导入,也支持其他原理图工具产生的网表导入。如下图所示为OrCAD所产生的网表:

在Allegro中导入网表的方式有两种:

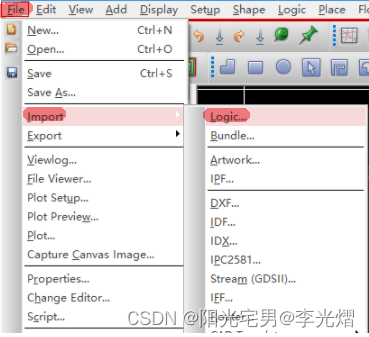

1.通过菜单栏File->Import->logic选项,打开网表导入框。如下图所示:

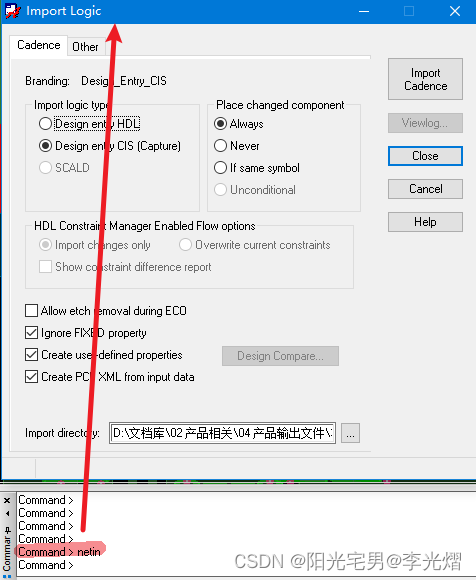

2.通过命令框(Command)输入netin打开网表导入框。如下图所示:

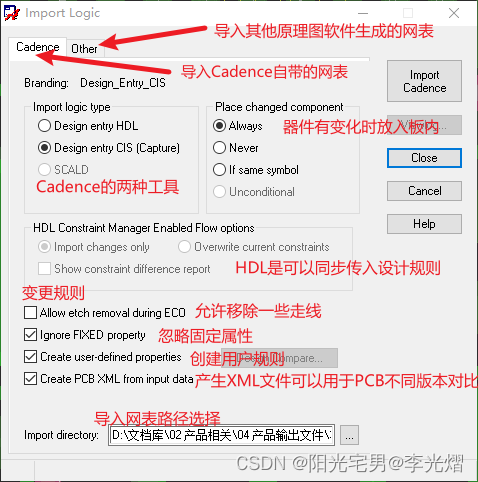

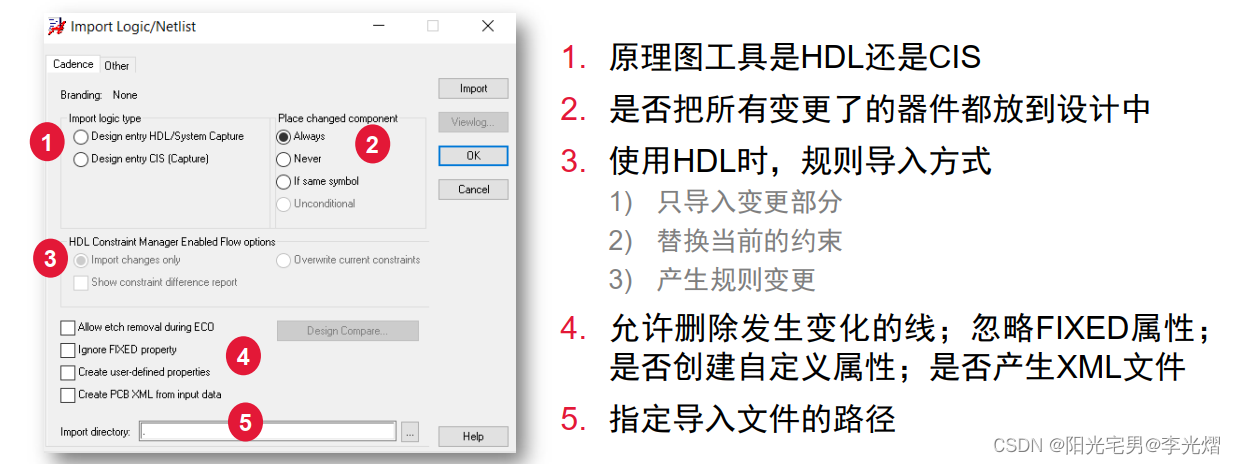

Allegro可导入的网表有多种形式,可以直接导入Cadence生成的网表文件,也可以导入其他原理图软件生成的网表文件。以下是Import Logic选项框的一些主要释义。因为小编主要是使用Cadence所以只列出导入Cadence生成的网表文件的一些重要选项的释义。

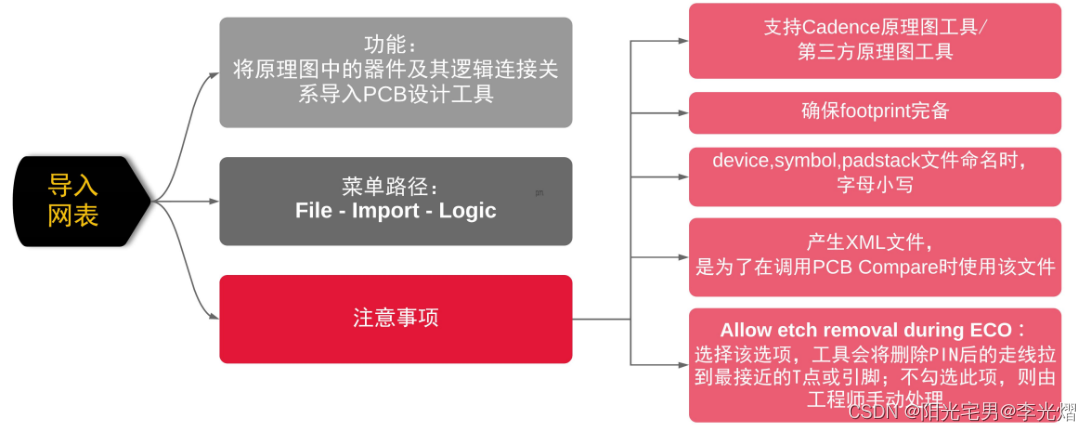

关于网表的导入可参考如下图所示的思维导图:

导入网表选项框中的主要释义如下:

如果是不导入设计规则,那么选择原理图工具为CIS。一般选择把所有变更器件都放入设计中,所以2选Always。变更规则部分根据实际需要去选择,一般我全部进行选择。有时我也不勾选Allow etch removal during选项,这样要自己处理板内变更的走线。

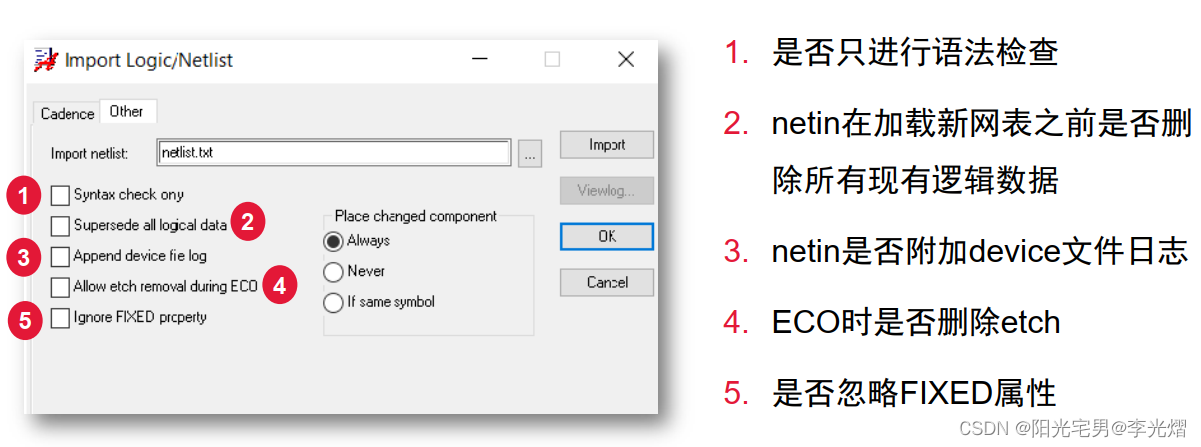

导入第三方网表输入框释义参考。

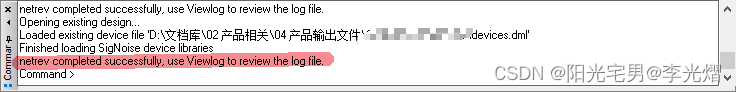

在网表导入框中点击Import,导入网表。当网表导入完成后在Command框中会显示如下信息。我们可以通过查看log文件来看导入是否正确。

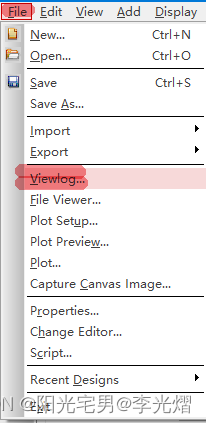

选择File->Viewlog选项,调出log窗口:

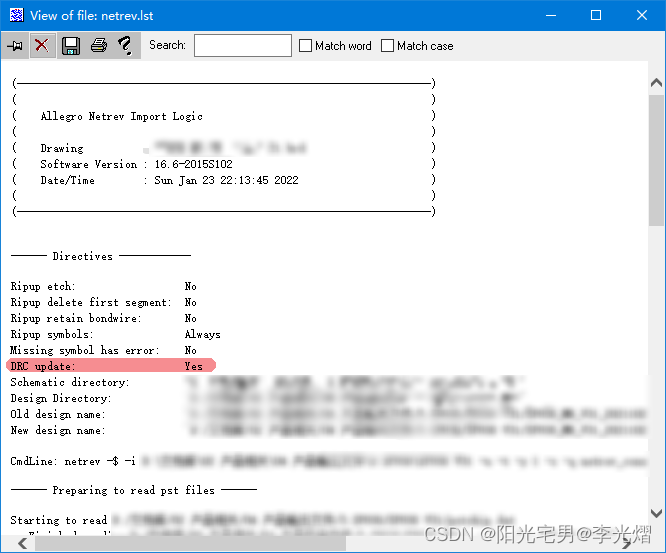

log会显示很多的信息,如下图所示,会显示drc是否有更新,导入的路径,导入的器件库路径,导入是否完善等等。

免责声明:本文系网络转载或改编,未找到原创作者,版权归原作者所有。如涉及版权,请联系删