我们原先聊过TB中的一些写法,会让VCS出现仿真错误。详情见我的这个视频: VCS仿真的注意事项,注意,观众评论区提出的方法也很重要,视频方法和评论区的方法都能解决问题。

但是,如果是TB风格导致的VCS仿错,而是RTL的设计思路不被VCS所理解,那该怎么办呢?

我们来说个具体案例:我有两个时钟,clkA,clkB。clkB是慢的,clkA是快的,clkB是clkA的分频。那么,按理说,clkB下面的信号和clkA下面的信号是同步的。但是,仿真的时候,VCS分不清楚,clkA下面的数据,上升沿,经常被clkB采到。这是不符合我们仿真要求的,我们仿真是不能采集一个数据的上升沿的,对吧。我过去的办法是把clkA向后挪几个ps,但是这个不是长久之计。我希望VCS能够知道clkA和clkB的同步关系,这样它就不会出现这种事情了。请问VCS有没有什么设置语法,可以明确告诉他这一点的?

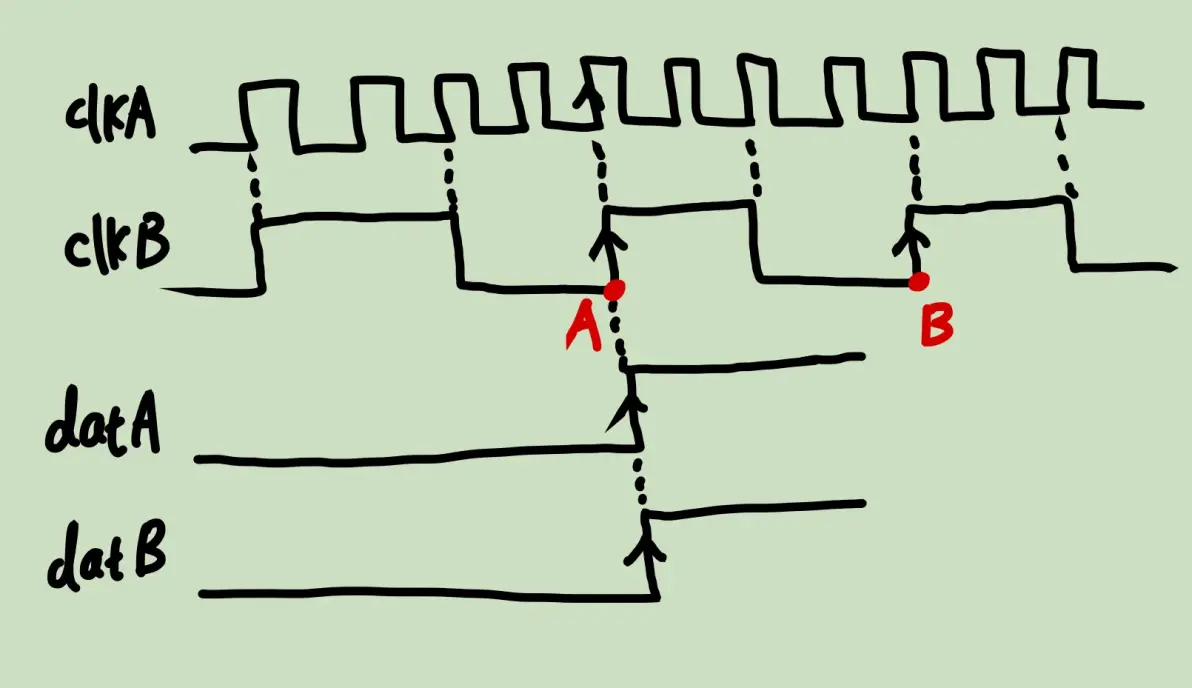

上面的问题如下图所示,datA属于clkA域,datA在A点上升,clkB与clkA完全同步,按理说它采样datA后,得到的datB应该在B点上升,但仿真中,datB也在A点上升,这是不对的。流出来片,一定是在B点上升的。

那这个前仿问题怎么解呢?我咨询了synopsys和cadence的AE,他们都说这种现象会发生,而且没有好的办法。我查了eetop等专业网站,也没有相关问题的帖子。所以就需要我们人为在RTL上做点工作,让仿真正确。

正确思路是:就是找到clkA和clkB交互过程中的关键信号,比如,clkA发出了一个sig,clkB会采这个sig。那就把sig延迟1ps(clkA发出的时候就延迟),这样就没问题了。

以上图为例,就是将datA在clkA打拍之后,在RTL上延迟1ps。这个延迟是不会被综合的,大家可以放心。

比较不好的办法是:如果延迟clkA,或者延迟clkB,让它俩存在1ps相位差的话,比较危险,会出现很窄的1ps的脉冲被采样到的情况。在时序分析上是不允许的。所以,我最终还是用延迟数据的方式,而不是延迟时钟,来解决这个问题。

武汉格发信息技术有限公司,格发许可优化管理系统可以帮你评估贵公司软件许可的真实需求,再低成本合规性管理软件许可,帮助贵司提高软件投资回报率,为软件采购、使用提供科学决策依据。支持的软件有: CAD,CAE,PDM,PLM,Catia,Ugnx, AutoCAD, Pro/E, Solidworks ,Hyperworks, Protel,CAXA,OpenWorks LandMark,MATLAB,Enovia,Winchill,TeamCenter,MathCAD,Ansys, Abaqus,ls-dyna, Fluent, MSC,Bentley,License,UG,ug,catia,Dassault Systèmes,AutoDesk,Altair,autocad,PTC,SolidWorks,Ansys,Siemens PLM Software,Paradigm,Mathworks,Borland,AVEVA,ESRI,hP,Solibri,Progman,Leica,Cadence,IBM,SIMULIA,Citrix,Sybase,Schlumberger,MSC Products...