软件

产品

事先声明,图是我们老师的PPT上截下来的,有水印,但是完全雨我无瓜

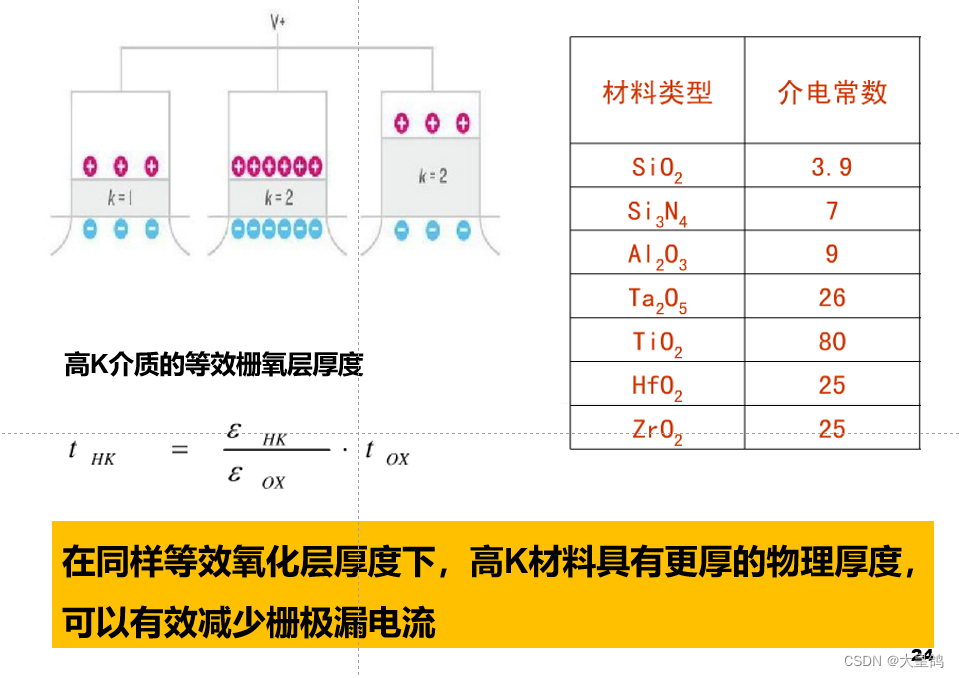

在芯片的发展过程中,作为氧化层的SIO2的厚度一降再降,这使得mos管的漏电流现象十分严重。为了防止漏电流的产生,就需要增加栅介质层的厚度。但是,由电容的计算 公式 我们会发现,如果将SiO2的厚度增加(那不是开历史的倒车么),介电常数不变,会使得栅氧化层的等效电容降低,如此一来,在同样的栅极电压下,形成的反型层的厚度必然要降低,这肯定是不利于导通的。

前者要求我们增加栅氧化层的 物理 厚度,所以我们只能选择介电常数更高的氧化介质。

本来我在想,既然你因为二氧化硅介质层的厚度降低产生明显漏电流了,这下又为了防止漏电流去增加厚度,甚至还更换了一种材料。我不是很理解这种迷惑行为,你一开始不要做那么薄不就可以了吗?(不过在上面这张图中,高K截止的 mos 管的栅极通过压缩栅极电极的低电阻层的方式保证了栅极的高度不变)

还有一种可能就是,一开始在 设计 二氧化硅介质层的厚度的时候,因为二氧化硅的低K,就需要将二氧化硅的厚度给设计的薄一点,以满足反型层厚度的需求,这时候便已经有些许的漏电流效应了,只是在升级工艺的过程中,需要更薄的氧化介质层,才进一步压榨二氧化硅的厚度,导致了更强的漏电流。

emmm,我觉得采用一种新的材料,并不是仅仅因为一个原因的。还有一个原因要换掉二氧化硅。

就是P型mos管的二氧化硅介质层的硼穿透效应。

免责声明:本文系网络转载或改编,未找到原创作者,版权归原作者所有。如涉及版权,请联系删