参见: https://blog.csdn.net/darknessdarkness/article/details/105140009

参见: https://blog.csdn.net/darknessdarkness/article/details/105140009

第二题:SV知识

bit可以用于合并数组的定义,合并数组的存储都是连续的,所以只能定义bit类型;

https://blog.csdn.net/zhajio/article/details/79529652

还没涉及

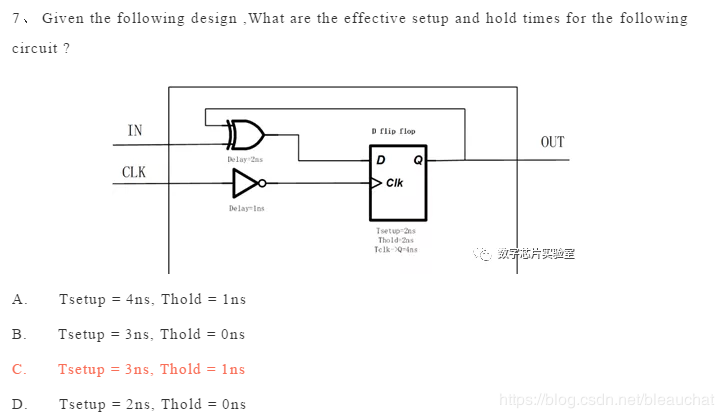

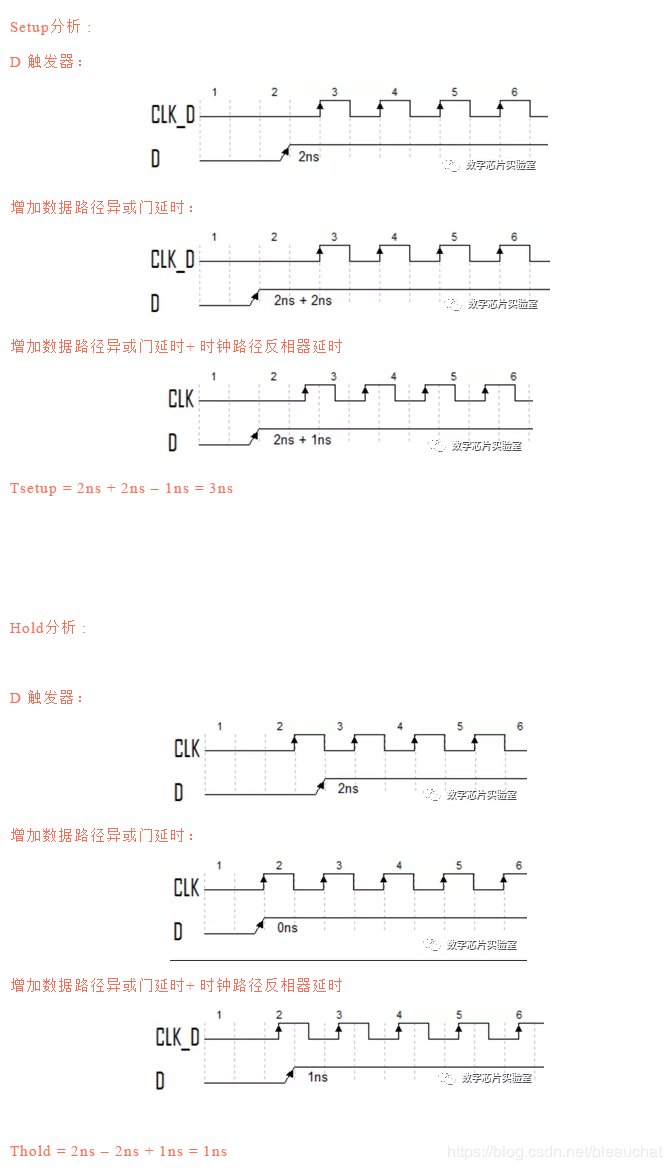

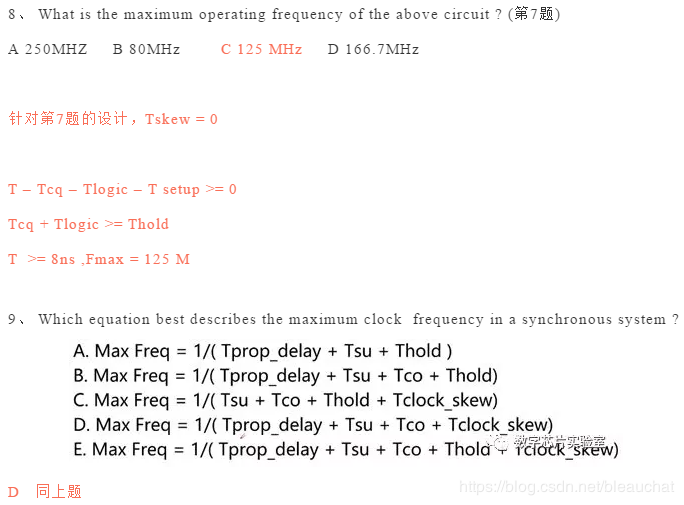

对于setup而言:

本级的clk_skew延时是有利的,(可以扩大design margin)

本级之前的comb逻辑延迟和clk_skew是不利的。

有利是指可以放宽要求,也就是往接近clk上升沿走。对于setup而言,最差情况是margin=0的点,也就是数据到达D端的时候刚好满足setup条件,此时本级skew可以预留出1ns的margin,所以setup可以放宽1ns(+)。相反,comb延迟使得数据往后推迟2ns,setup需要变紧(-)。

所以setup’ = setup + 1 - 2

对于hold而言:

本级的clk_skew是不利的(缩小了design margin)

本级之前的comb延时和clk_skew是有利的。

对于hold而言,最差情况是margin=0的点,也就是数据在上升沿后hold时间刚好改变,此时本级skew会使数据等效地提前1ns,也就是hold的检查点会提前1ns,所以要不发生violation,hold需要变紧1ns(+)。相反,comb延迟使得数据往后推迟2ns,hold可以放宽2ns(-)。

所以hold’ = hold + 1 - 2

对于这种DFF的输出还会接回到自己的例子,因为这条path的clk其实是同一个clk,所以clk skew = 0。

</div><div><div></div></div>

<link href="https://csdnimg.cn/release/phoenix/mdeditor/markdown_views-ff98e99283.css" rel="stylesheet">

</div>

免责声明:本文系网络转载或改编,未找到原创作者,版权归原作者所有。如涉及版权,请联系删