在设计普通电路或低速信号电子产品时,都是PCB供应商给工程师提供一份层叠结构,工程师照搬照用就行,但是由于信号速度的增加、产品差异化更多、产品认证要求增多,因此PCB设计工程师需要掌握更多叠层设计方面的知识,以应对这些产品变化所带来的问题。

层叠设计是一个系统的工作,需要考虑的因素比较多,如PCB需要多厚才能符合结构设计和应力的要求;多少个信号层才能满足产品的布线要求;铜箔需要多厚;多少个电源平面才能满足产品的电源完整性要求;PCB上有多少类不同的阻抗线才能满足不同总线阻抗的要求;需要什么级别的基板材料才能满足总线的传输要求;哪一类表面处理工艺才能满足产品在某些特定的环境中使用等等。

PCB的层叠设计对整个系统的EMC设计也起着非常重要的作用,良好的叠层可以有效的减小PCB回路的辐射效应,所以层叠设计关系到信号的完整性、电源完整性、电磁兼容性、结构、散热等方面的设计,当然还有一个非常重要的就是成本的问题。

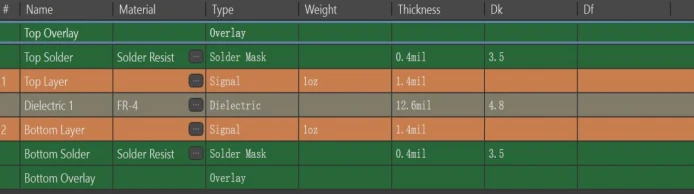

对于两层板来说,由于板层数量少,已经不存在叠层的问题。控制EMI辐射主要从布线和布局来考虑;

双层板通常使用在低于10KHz的低频模拟设计中:

1)在同一层的电源走线以辐射状走线,并最小化线的长度总和;

2)走电源、地线时,相互靠近;在关键信号线边上布一条地线,这条地线应尽量靠近信号线。这样就形成了较小的回路面积,减小差模辐射对外界干扰的敏感度。当信号线的旁边加一条地线后,就形成了一个面积最小的回路,信号电流肯定会取道这个回路,而不是其它地线路径。

3)如果是双层线路板,可以在线路板的另一面,紧靠近信号线的下面,沿着信号线布一条地线,一线尽量宽些。这样形成的回路面积等于线路板的厚度乘以信号线的长度。

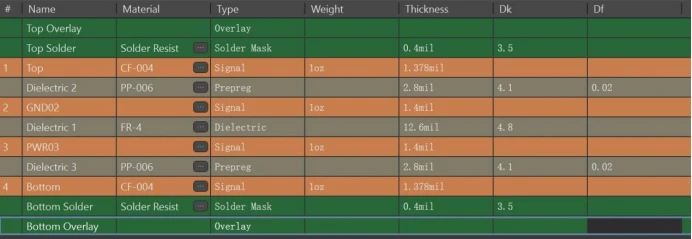

1)Top-GND02-PWR03-Bottom;

第一种方案,通常应用于板上芯片较多的情况。这种方案可得到较好的SI性能,对于EMI性能来说并不是很好,主要要通过走线及其他细节来控制。主要注意:地层放在信号最密集的信号层的相连层,有利于吸收和抑制辐射;增大板面积,体现20H规则。

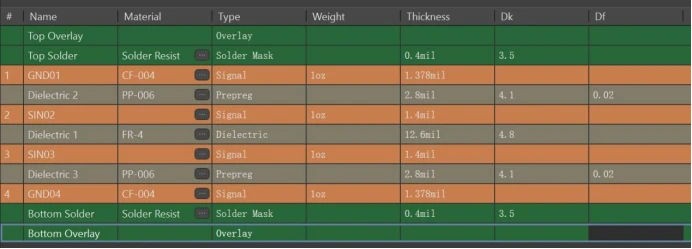

2)GND01-SIN02-SIN03-GND04;

对于第二种方案,通常应用于板上芯片密度足够低和芯片周围有足够面积(放置所要求的电源覆铜层)的场合。此种方案PCB的外层均为地层,中间两层均为信号/电源层。信号层上的电源用宽线走线,这可使电源电流的路径阻抗低,且信号微带路径的阻抗也低,也可通过外层地屏蔽内层信号辐射。从EMI控制的角度看,这是现有的最佳4层PCB结构。

对于以上两种叠层设计,潜在的问题是对于传统的1.6mm(62mil)板厚。层间距将会变得很大,不仅不利于控制阻抗,层间耦合及屏蔽;特别是电源地层之间间距很大,降低了板电容,不利于滤除噪声。

主要注意:中间两层信号、电源混合层间距要拉开,走线方向垂直,避免出现串扰;适当控制板面积,体现20H规则;如果要控制走线阻抗,上述方案要非常小心地将走线布置在电源和接地铺铜岛的下边。另外,电源或地层上的铺铜之间应尽可能地互连在一起,以确保DC和低频的连接性。

对于芯片密度较大、时钟频率较高的设计应考虑6层板的设计,推荐叠层方式:

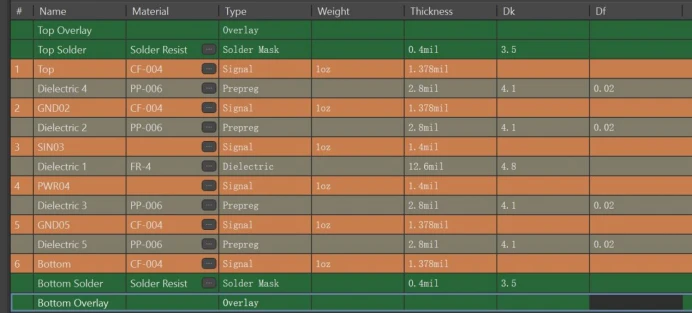

1)Top-GND02-SIN03-PWR04-GND05-Bottom;

对于这种方案,这种叠层方案可得到较好的信号完整性,信号层与接地层相邻,电源层和接地层配对,每个走线层的阻抗都可较好控制,且两个地层都是能良好的吸收磁力线。并且在电源、地层完整的情况下能为每个信号层都提供较好的回流路径。

2)GND01-SIN02-GND03-PWR04-SIN05-GND06;

对于这种方案,该种方案只适用于器件密度不是很高的情况,这种叠层具有上面叠层的所有优点,并且这样顶层和底层的地平面比较完整,能作为一个较好的屏蔽层 来使用。需要注意的是电源层要靠近非主元件面的那一层,因为底层的平面会更完整。因此,EMI性能要比第一种方案好。

对于六层板的方案,电源层与地层之间的间距应尽量减小,以获得好的电源、地耦合。但62mil的板厚,层间距虽然得到减小,还是不容易把主电源与地层之间的间距控制得很小。对比第一种方案与第二种方案,第二种方案成本要大大增加。因此,我们叠层时通常选择第一种方案。设计时,遵循20H规则和镜像层规则设计。

1)第一种叠层方式由于差的电磁吸收能力和大的电源阻抗导致这种不是一种好的叠层方式。它的结构如下:

2)第二种叠层方式的变种,由于增加了参考层,具有较好的EMI性能,各信号层的特性阻抗可以很好的控制:

3)最佳叠层方式,由于多层地参考平面的使用具有非常好的地磁吸收能力。

以上就是二层板至八层板的层叠方案,我们虽然只介绍了二层到八层板的叠层,但是对于更高层数的PCB叠层我们也可以这样分析一下,结合板子密度和结构确定层数,再根据层数选取一个合适的层叠方案。

对于如何选择设计用几层板和用什么方式的叠层,要根据板上信号网络的数量、器件密度、PIN密度、信号的频率、板的大小等许多因素综合考虑。对于信号网络的数量越多,器件密度越大,PIN密度越大,信号的频率越高的设计应尽量采用多层板设计。为得到好的EMI性能最好保证每个信号层都有自己的参考层。

免责声明:本文系网络转载或改编,未找到原创作者,版权归原作者所有。如涉及版权,请联系删

武汉格发信息技术有限公司,格发许可优化管理系统可以帮你评估贵公司软件许可的真实需求,再低成本合规性管理软件许可,帮助贵司提高软件投资回报率,为软件采购、使用提供科学决策依据。支持的软件有: CAD,CAE,PDM,PLM,Catia,Ugnx, AutoCAD, Pro/E, Solidworks 等。