在工作中经常会遇到有人问什么是高速电路,或者在设计高速电路的时候需要注意什么。每当遇到这种问题就头脑发懵,其实不同的产品、不同的人对其都有不同的理解。今天简单总结一下最基本的一些概念包括对高速电路的理解、什么是信号完整性还有信号的带宽等。

一、高速电路的定义

本人从各种资料和书中看到许多关于高速电路的定义,可能不同的产品对于高速信号的定义不同,具体还要看设计的产品类型,简单整理主要有以下几种:

1.是指由于信号的高速变化使电路中的模拟特性,如导线的电感、电容等发生作用的电路。

2.信号工作频率超过50MHz,并且在这个频率之上的电路已经占到了整个电子系统相当的分量。

3.根据信号的上升沿和下降沿的时间来定义。

4.大家通常比较熟悉的DDR、Serdes、UFS等一些上G传输速率的layout等。

二、信号完整性问题

信号完整性要求就是信号从发送端到互连传输过程中以正确的时序、幅度及相位到达接受端,并且接受端能正常的工作,或者可以说信号在互连传输中能很好的保持时域和频域的特性。通常还有以下两种定义:

1.当信号的边沿时间小于4-6倍的互连传输时延,需要考虑信号的完整性问题。

2.当线传播时延大于驱动端的上升沿或下降沿将会引起传输的非预期的结果。

3.下面在简单说下时域和频域的关系,因为当初本人接触到这两个概念是一头雾水,很懵:

**时域**:是真实世界的,指的是时间域,自变量是时间。

**频域**:是用于分析时域的一种方法,指的是频率域,自变量是频率。

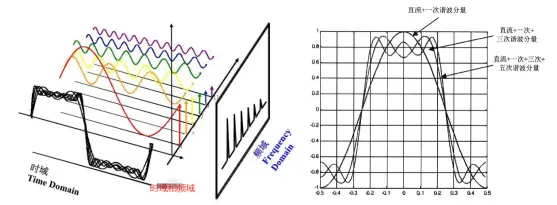

动态信号从时间域变换到频率域主要通过傅里叶级数和傅里叶变换实现。周期信号靠傅里叶级数,非周期信号靠傅里叶变换。下面这个图片是从网上下载的,大家可以理解一下,本人感觉从以上傅里叶变换自己是很难理解的:

三、信号带宽

1.定义:信号的带宽就是信号频谱的宽度,也就是信号的最高频率分量与最低频率之差。

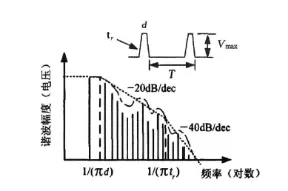

带宽的选择对信号的时域波形的信号沿的上升时间有直接的影响,带宽越大,信号的上升的时间就越短。在信号传输过程中如果可以保证信号的带宽(BW=0.35/RT)以下的频率分量经过的互连路径质量,则可以相对较好的保证信号质量。下面可能涉及到两个公式:

2.信号的带宽=0.35/信号边升沿时间,其中边沿时间的单位为ns,信号的带宽可以理解为信号的最高次谐波的频率,单位为MHz。

3..F=1/Πtr,这个公式由以下图片(Cadence 高速电路设计)得来。这两个公式是相同概念,可以近似的计算带宽或上升沿时间。

以上资料主要参考《Cadence 高速电路设计》、《ANSYS信号完整性分析与仿真实例》

如有雷同或错误,希望各位大神留言指正,感谢!!!

更多课程资料,免费试听,保存二维码到微信扫一扫添加

武汉格发信息技术有限公司,格发许可优化管理系统可以帮你评估贵公司软件许可的真实需求,再低成本合规性管理软件许可,帮助贵司提高软件投资回报率,为软件采购、使用提供科学决策依据。支持的软件有: CAD,CAE,PDM,PLM,Catia,Ugnx, AutoCAD, Pro/E, Solidworks 等。